# **Unit 6: Testing**

- Course contents

- Fault Modeling

- Fault Simulation

- Test Generation

- Design For Testability

- Reading

Supplementary readings

# Outline

#### Introduction

- Fault Modeling

- Fault Simulation

- Test Generation

- Design For Testability

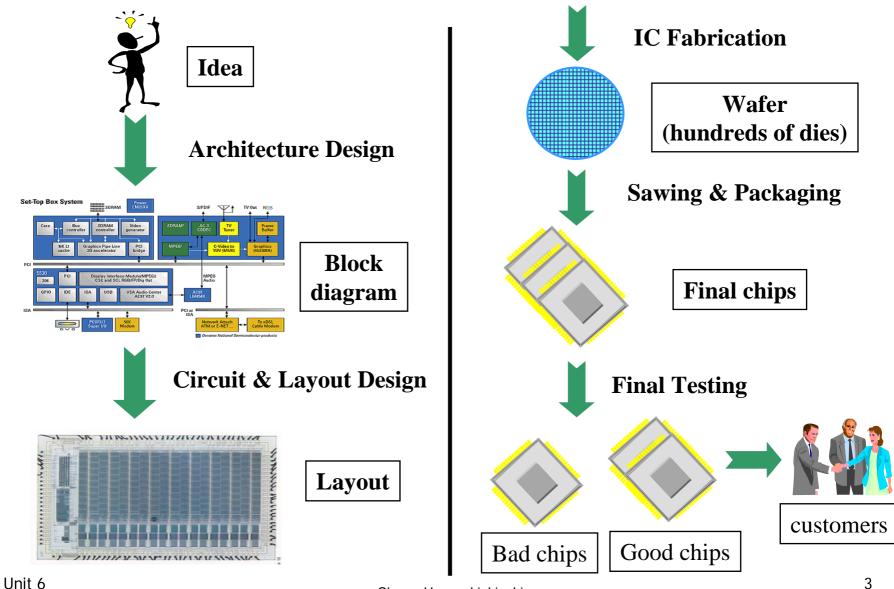

#### **Chip Design & Manufacturing Flow**

# **Design Verification, Testing and Diagnosis**

- Design Verification:

- Ascertain the design perform its specified behavior

- Testing:

- Exercise the system and analyze the response to ascertain whether it behaves correctly after manufacturing

- Diagnosis:

- To locate the cause(s) of misbehavior after the incorrect behavior is detected

#### **Manufacturing Defects**

- Processing Faults

- missing contact windows

- parasitic transistors

- oxide breakdown

- Material Defects

- bulk defects (cracks, crystal imperfections)

- surface impurities

- Time-Dependent Failures

- dielectric breakdown

- electro-migration

- Packaging Failures

- contact degradation

- seal leaks

#### **Faults, Errors and Failures**

- Fault:

- A physical defect within a circuit or a system

- May or may not cause a system failure

- Error:

Manifestation of a fault that results in incorrect circuit (system) outputs or states

- Caused by faults

- Failure:

- Deviation of a circuit or system from its specified behavior

- Fails to do what it should do

- Caused by an error

- Fault ---> Error ---> Failure

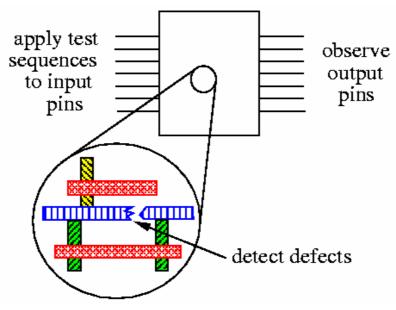

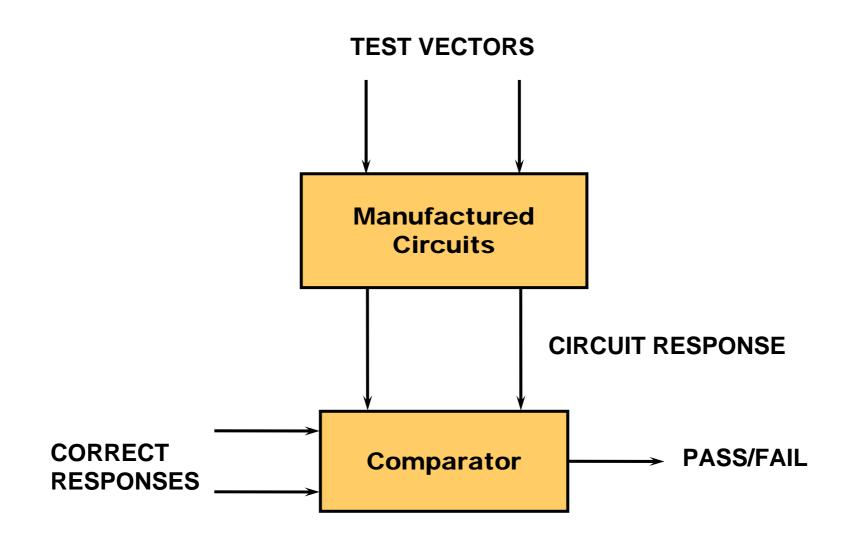

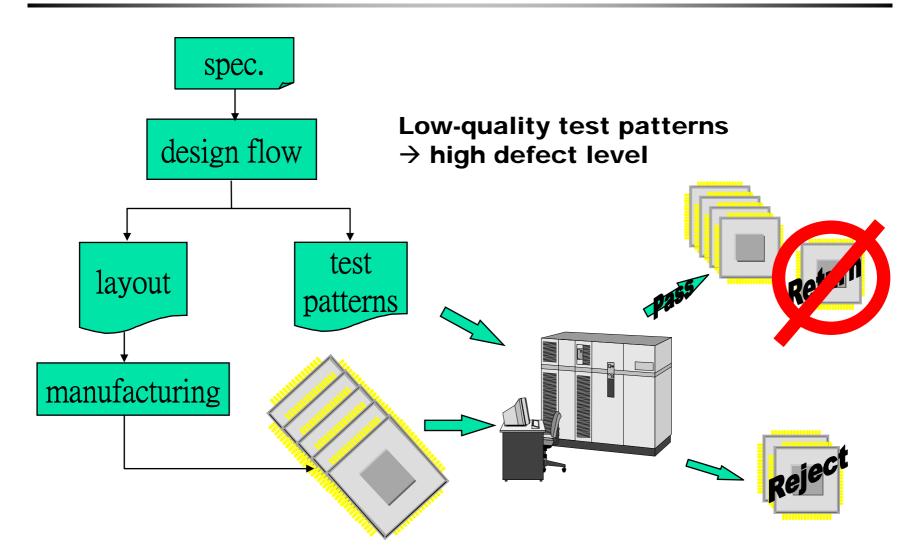

#### **Scenario of Manufacturing Test**

#### **Tester: Advantest T6682**

### **Purpose of Testing**

- Verify Manufacturing of Circuit

- Improve System Reliability

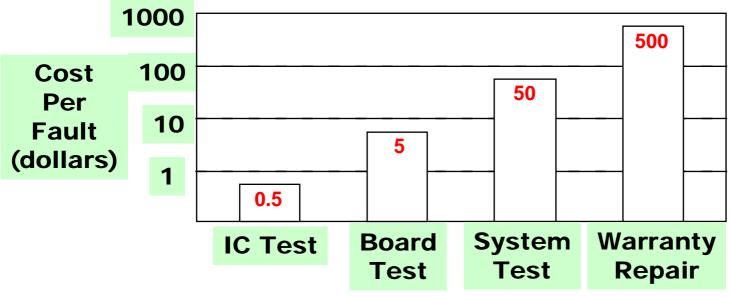

- Diminish System Cost

- Cost of repair

- goes up by an order of magnitude each step away from the fab. line

B. Davis, "The Economics of Automatic Testing" McGraw-Hill 1982

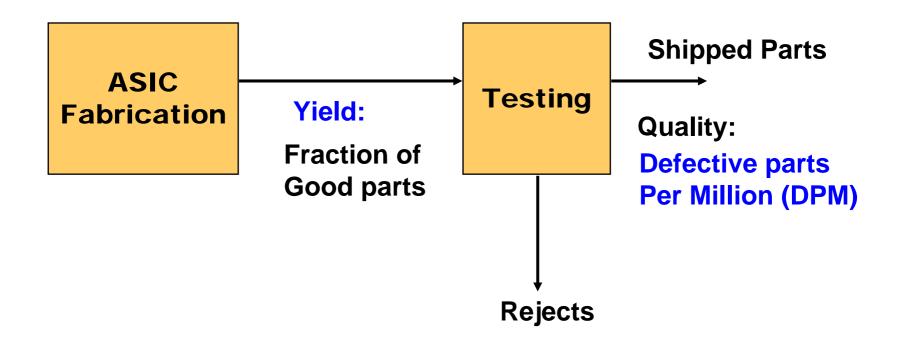

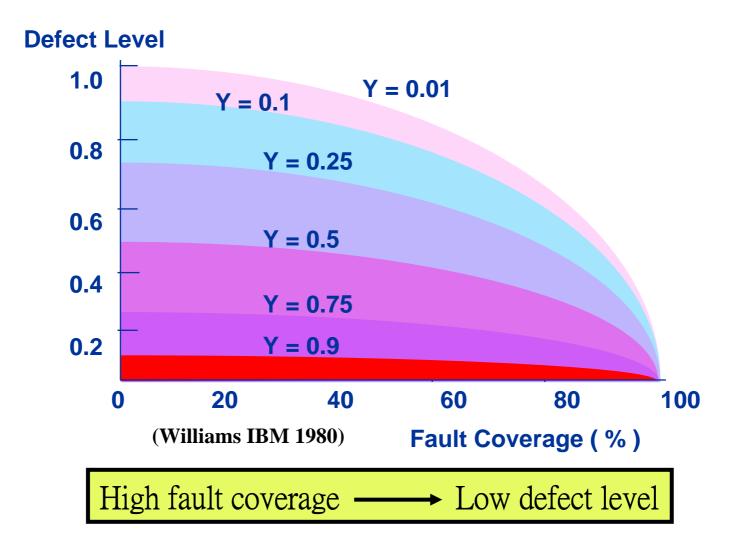

# **Testing and Quality**

# Quality of shipped part is a function of yield Y and the test (fault) coverage T.

- Fault Coverage T

- Is the measure of the ability of a set of tests to detect a given class of faults that may occur on the device under test (DUT)

# $T = \frac{No. of detected faults}{No. of all possible faults}$

• Defect Level

Is the fraction of the shipped parts that are defective

$$DL = 1 - Y^{(1-T)}$$

Y: yield T: fault coverage

#### **DPM v.s. Yield and Coverage**

| Yield | Fault Coverage | DPM    |

|-------|----------------|--------|

| 50%   | 90%            | 67,000 |

| 75%   | 90%            | 28,000 |

| 90%   | 90%            | 10,000 |

| 95%   | 90%            | 5,000  |

| 99%   | 90%            | 1,000  |

| 90%   | 90%            | 10,000 |

| 90%   | 95%            | 5,000  |

| 90%   | 99%            | 1,000  |

| 90%   | 99.9%          | 100    |

# Why Testing Is Difficult ?

- Test application time can be exploded for exhaustive testing of VLSI

- For a combinational circuit with 50 inputs, we need  $2^{50} = 1.126 \times 10^{15}$  test patterns.

- Assume one test per  $10^{-7}$ sec, it takes  $1.125 \times 10^{8}$ sec = 3.57yrs. to test such a circuit.

- Test generation for sequential circuits are even more difficult due to the lack of controllability and observability at flip-flops (latches)

- Functional testing

- may NOT be able to detect the physical faults

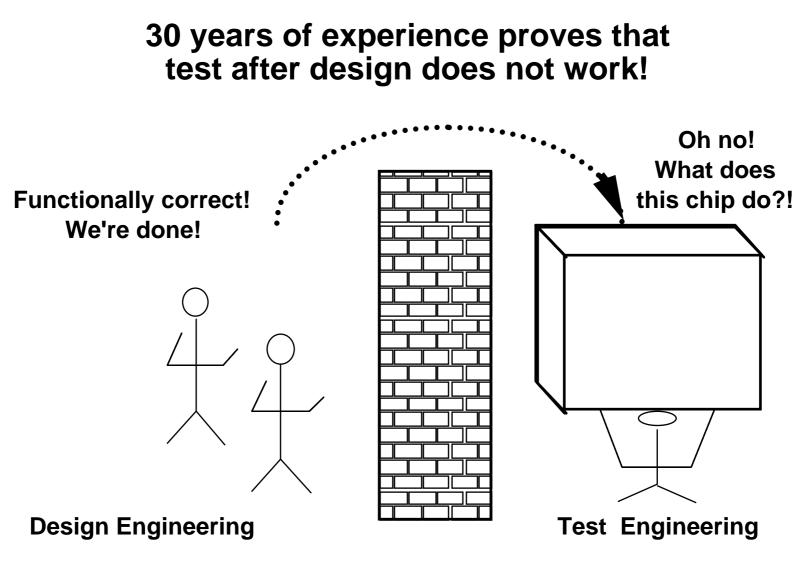

#### **The Infamous Design/Test Wall**

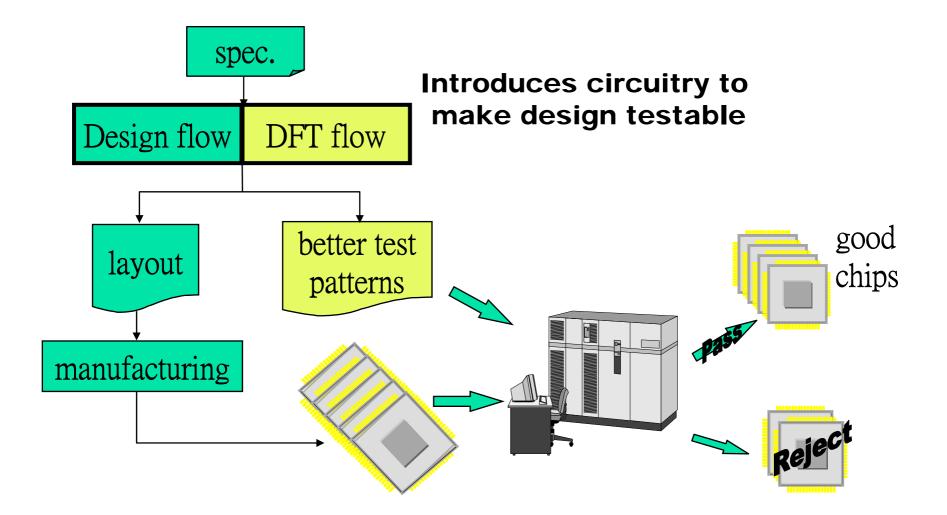

#### **Old Design & Test Flow**

#### **New Design and Test Flow**

# Outline

- Introduction

- Fault Modeling

- Fault Simulation

- Test Generation

- Design For Testability

#### **Functional v.s. Structural Testing**

- I/O function tests inadequate for manufacturing

Functionality vs. component & interconnection testing

- Exhaustive testing is Prohibitively expensive

#### Why Fault Model ?

- Fault model identifies target faults

- Model faults most likely to occur

- Fault model limits the scope of test generation

- Create tests only for the modeled faults

- Fault model makes effectiveness measurable by experiments

- Fault coverage can be computed for specific test patterns to reflect its effectiveness

- Fault model makes analysis possible

- Associate specific defects with specific test patterns

# **Fault Modeling**

#### • Fault Modeling

Model the effects of physical defects on the logic function and timing

#### • Physical Defects

- Silicon Defects

- Photolithographic Defects

- Mask Contamination

- Process Variation

- Defective Oxides

#### Fault Modeling (cont'd)

- Electrical Effects

- Shorts (Bridging Faults)

- Opens

- Transistor Stuck-On/Open

- Resistive Shorts/Opens

- Change in Threshold Voltages

#### Logical Effects

- Logical Stuck-at 0/1

- Slower Transition (Delay Faults)

- AND-bridging, OR-bridging

#### Fault Types Commonly Used To Guide Test Generation

- Stuck-at Faults

- Bridging Faults

- Transistor Stuck-On/Open Faults

- Delay Faults

- IDDQ Faults

- State Transition Faults (for FSM)

- Memory Faults

- PLA Faults

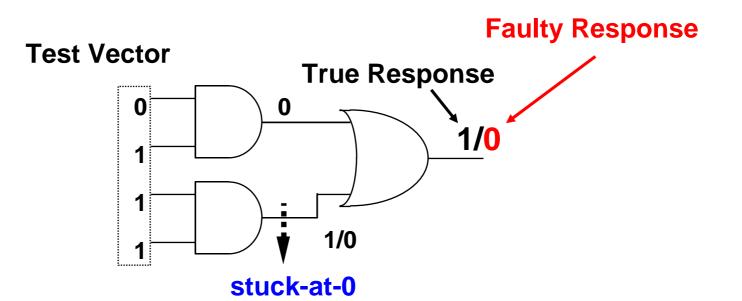

#### **Single Stuck-At Fault**

#### **Assumptions:**

- Only One line is faulty

- Faulty line permanently set to 0 or 1

- Fault can be at an input or output of a gate

#### **Multiple Stuck-At Faults**

- Several stuck-at faults occur at the same time

Important in high density circuits

- For a circuit with k lines

- there are 2k single stuck-at faults

- there are 3<sup>k</sup>-1 multiple stuck-at faults

- A line could be stuck-at-0, stuck-at-1, or fault-free

- One out of 3<sup>k</sup> resulting circuits is fault-free

#### Why Single Stuck-At Fault Model

- Complexity is greatly reduced

- Many different physical defects may be modeled by the same logical single stuck-at fault

- Stuck-at fault is technology independent

- Can be applied to TTL, ECL, CMOS, BiCMOS etc.

- Design style independent

- Gate array, standard cell, custom VLSI

- Detection capability of un-modeled defects

- Empirically many defects accidentally detected by test derived based on single stuck-at fault

- Cover a large percentage of multiple stuck-at faults

#### **Multiple Faults**

- Multiple stuck-fault coverage by single-fault tests of combinational circuit:

- 4-bit ALU (Hughes & McCluskey, ITC-84)

All double and most triple-faults covered.

- Large circuits (Jacob & Biswas, ITC-87)

Almost 100% multiple faults covered for circuits with 3 or more outputs.

- No results available for sequential circuits.

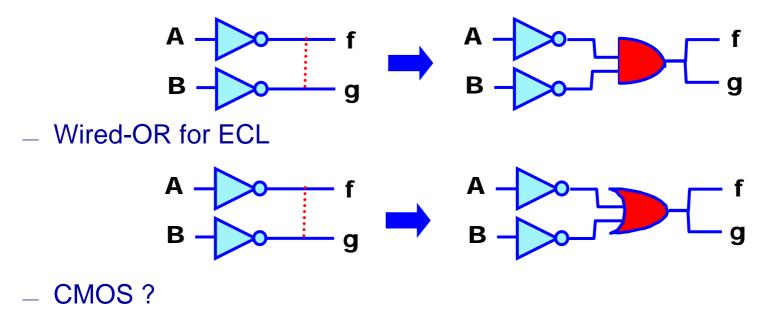

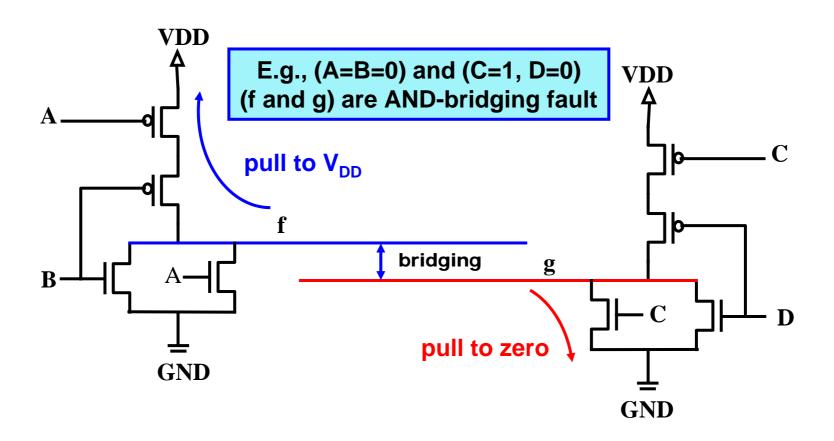

# **Bridging Faults**

- Two or more normally distinct points (lines) are shorted together

- Logic effect depends on technology

- Wired-AND for TTL

#### **Bridging Faults For CMOS Logic**

- The result

- could be AND-bridging or OR-bridging

- depends on the the inputs

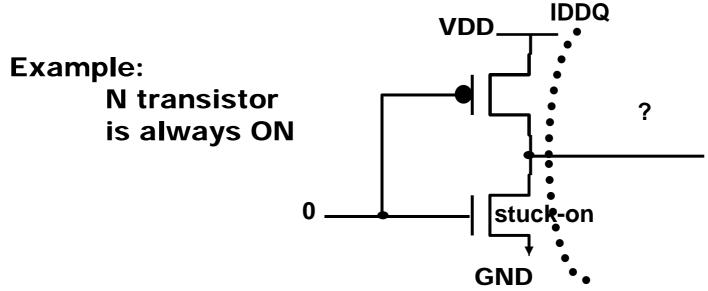

#### **CMOS Transistor Stuck-On**

- Transistor Stuck-On

- May cause ambiguous logic level

- Depends on the relative impedances of the pull-up and pulldown networks

- When Input Is Low

- Both P and N transistors are conducting, causing increased quiescent current, called IDDQ fault

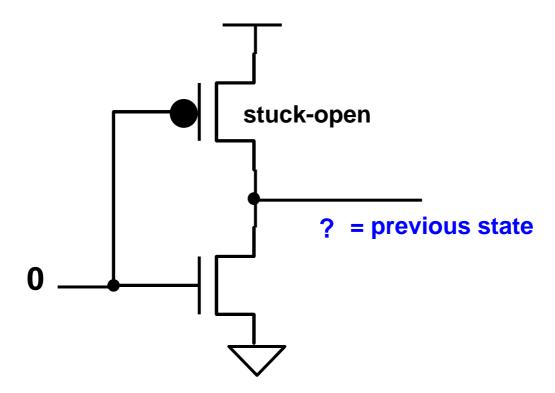

#### **CMOS Transistor Stuck-Open (I)**

- Transistor stuck-open

- May cause the output to be floating

- The faulty becomes exhibits sequential behavior

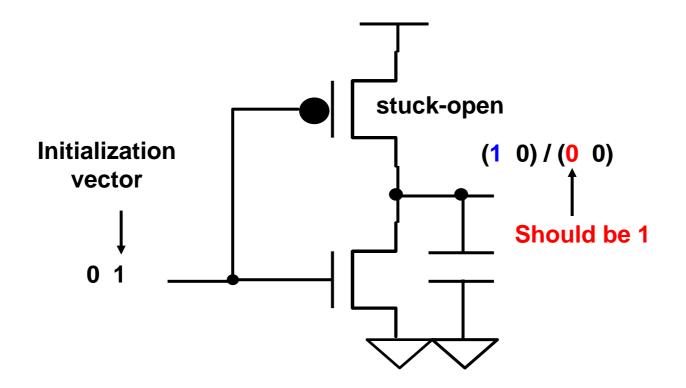

#### **CMOS Transistor Stuck-Open (II)**

- The circuit may turn into a sequential one

- Stuck-open requires two vector tests

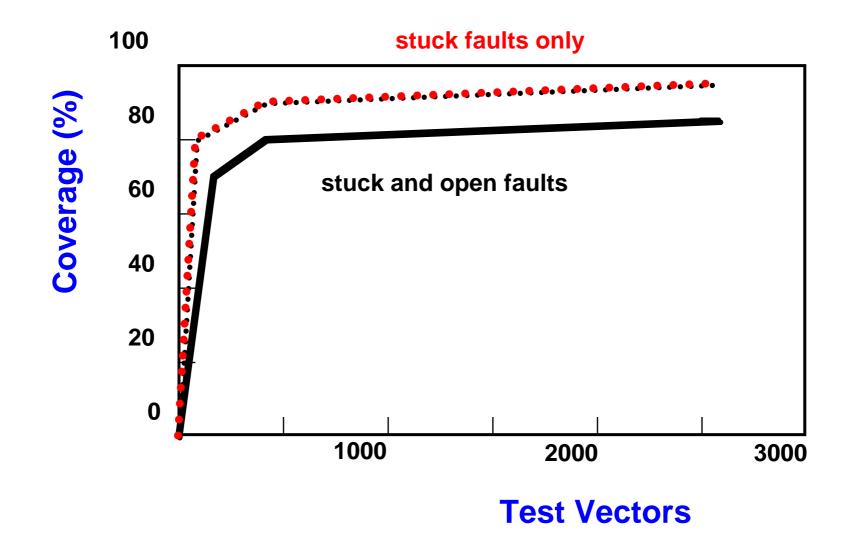

#### Fault Coverage in a CMOS Chip

#### **Summary of Stuck-Open Faults**

• First Report:

- Wadsack, Bell System Technology, J., 1978

- Recent Results

- Woodhall et. al, ITC-87 (1-micron CMOS chips)

- 4552 chips passed parametric test

- 1255 chips (27.57%) failed tests for stuck-at faults

- 44 chips (0.97%) failed tests for stuck-open faults

- 4 chips with stuck-open faults passed tests for stuck-at faults

- Conclusion

- Stuck-at faults are about 20 times more frequent than stuck-open faults

- About 91% of chips with stuck-open faults may also have stuckat faults

- Faulty chips escaping tests for stuck-at faults = 0.121%

#### **Memory Faults**

- Parametric Faults

- Output Levels

- Power Consumption

- Noise Margin

- Data Retention Time

- Functional Faults

- Stuck Faults in Address Register, Data Register, and Address Decoder

- Cell Stuck Faults

- Adjacent Cell Coupling Faults

- Pattern-Sensitive Faults

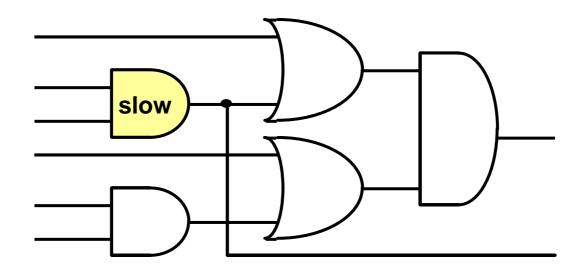

# **Delay Testing**

- Chip with timing defects

- may pass the DC stuck-fault testing, but fail when operated at the system speed

- For example, a chip may pass testing under 10 MHz operation, but fail under 100 MHz

- Delay Fault Models

- Gate-Delay Fault

- Path-Delay Fault

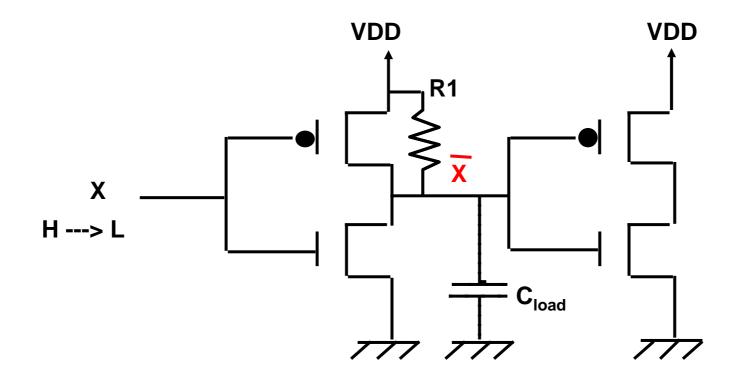

#### **Gate-Delay Fault**

- Slow to rise, slow to fall

- $-\overline{x}$  is slow to rise when channel resistance R1 is abnormally high

## **Gate-Delay Fault (cont'd)**

- Test Based on Gate-Delay Fault

- May not detect those delay faults that result from the accumulation of a number of small incremental delay defects along a path !! (Disadvantage)

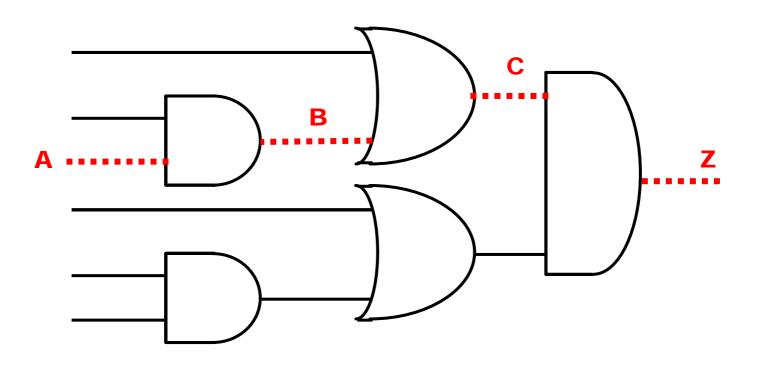

## **Path-Delay Fault**

- Associated with a Path (e.g. A-B-C-Z)

- Whose delay exceeds the clock interval

- More complicated than gate-delay fault

- Because the number of paths grows exponentially

# Why Logical Fault Modeling ?

- Fault analysis on logic rather than physical problem

Complexity is reduced

- Technology independent

- Same fault model is applicable to many technologies

- Testing and diagnosis methods remain valid despite changes in technology

- Tests derived

- may be used for physical faults whose effect on circuit behavior is not completely understood or too complex to be analyzed

- Stuck-at fault is

- The most popular logical fault model

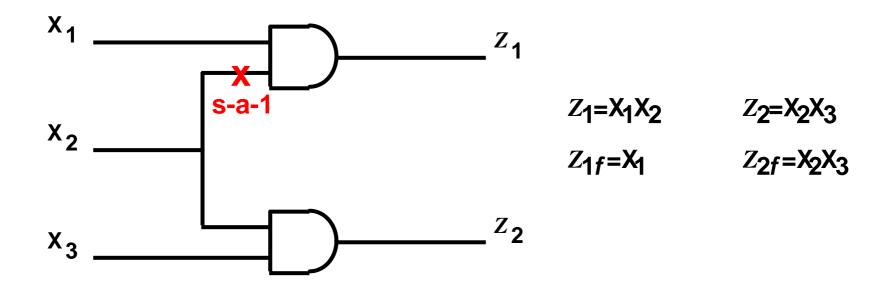

## **Definition Of Fault Detection**

- A test (vector) t detects a fault f iff

t detects f ⇔ z(t) ≠ z<sub>f</sub>(t)

- Example

The test (x1,x2,x3) = (100) detects *f* because  $z_1(100)=0$  while  $z_{1f}(100)=1$

## **Fault Detection Requirement**

- A test *t* that detects a fault *f*

- Activates f (or generate a fault effect) by creating different vand  $v_f$  values at the site of the fault

- Propagates the error to a primary output w by making all the lines along at least one path between the fault site and w have different v and  $v_f$  values

- Sensitized Line:

- A line whose value in response to the test changes in the presence of the fault *f* is said to be sensitized by the test in the faulty circuit

- Sensitized Path:

- A path composed of sensitized lines is called a sensitized path

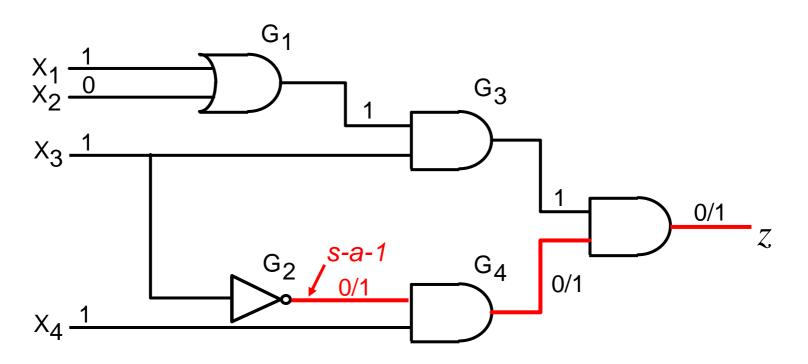

## **Fault Sensitization**

z (1011)=0  $z_f$  (1011)=1 1011 detects the fault f (G<sub>2</sub> stuck-at 1)  $v/v_f$ : v = signal value in the fault free circuit  $v_f$  = signal value in the faulty circuit

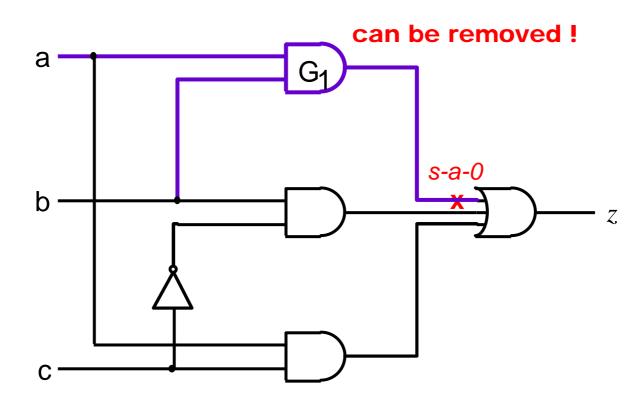

- A fault *f* is said to be detectable

- if there exists a test *t* that detects *f*; otherwise,

- f is an undetectable fault

- For an undetectable fault f

- No test can simultaneously activate *f* and create a sensitized path to a primary output

#### **Undetectable Fault**

- G<sub>1</sub> output stuck-at-0 fault is undetectable

- Undetectable faults do not change the function of the circuit

- The related circuit can be deleted to simplify the circuit

## **Test Set**

- Complete detection test set:

- A set of tests that detect any detectable faults in a class of faults

- The quality of a test set

- is measured by fault coverage

- Fault coverage:

- Fraction of faults that are detected by a test set

- The fault coverage

- can be determined by fault simulation

- >95% is typically required for single stuck-at fault model

- >99.9% in IBM

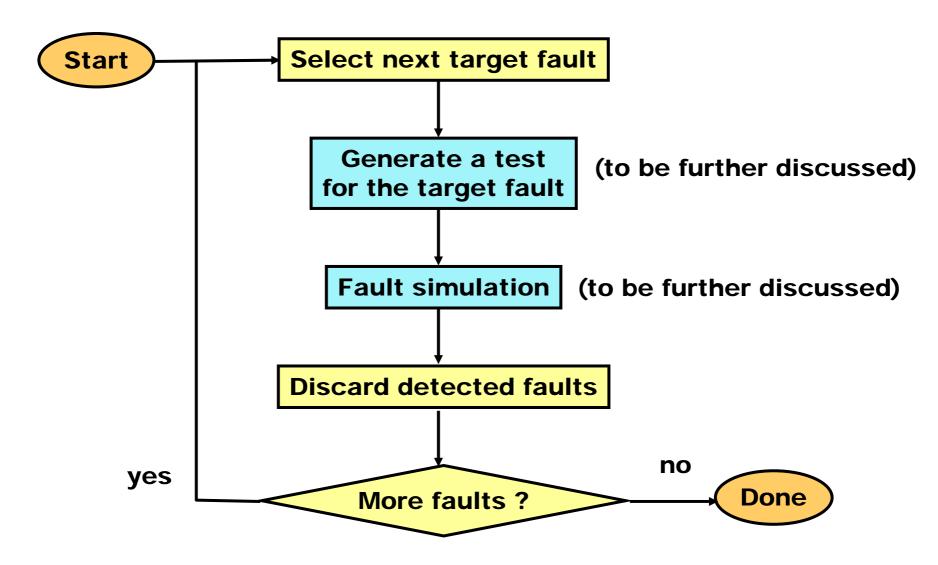

## **Typical Test Generation Flow**

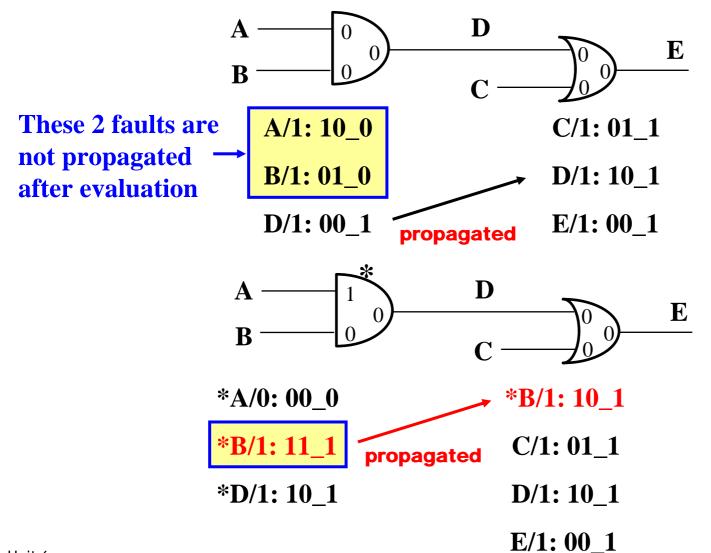

## **Fault Equivalence**

• Distinguishing test

– A test *t* distinguishes faults  $\alpha$  and  $\beta$  if

$$Z_{\alpha}(t) \oplus Z_{\beta}(t) = 1$$

- Equivalent Faults

- Two faults,  $\alpha \& \beta$  are said to be equivalent in a circuit, iff the function under  $\alpha$  is equal to the function under  $\beta$  for any input combination (sequence) of the circuit.

- No test can distinguish between  $\alpha$  and  $\beta$

- In other words, test-set( $\alpha$ ) = test-set( $\beta$ )

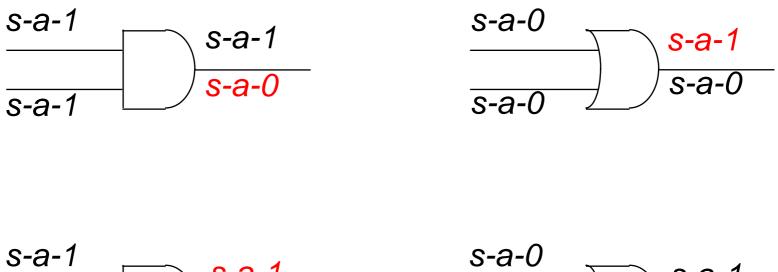

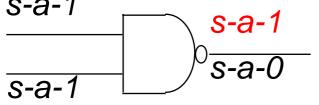

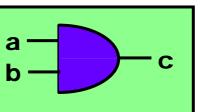

## **Fault Equivalence**

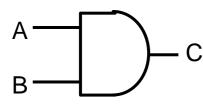

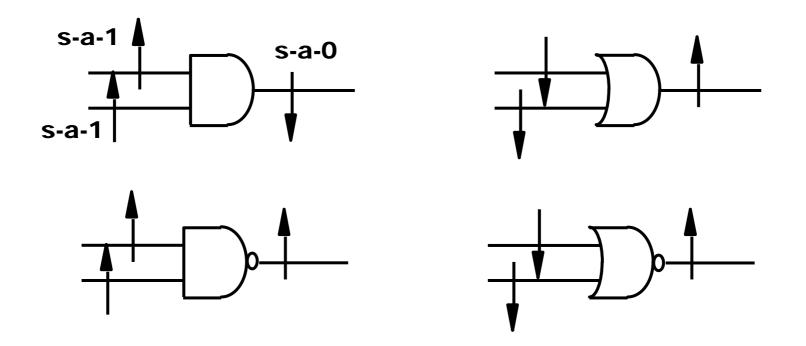

• AND gate:

- all s-a-0 faults are equivalent

- OR gate:

- all s-a-1 faults are equivalent

- NAND gate:

- all the input *s-a-0* faults and the output *s-a-1* faults are equivalent

- NOR gate:

- all input s-a-1 faults and the output s-a-0 faults are equivalent

- Inverter:

- input s-a-1 and output s-a-0 are equivalent input s-a-0 and output s-a-1 are equivalent

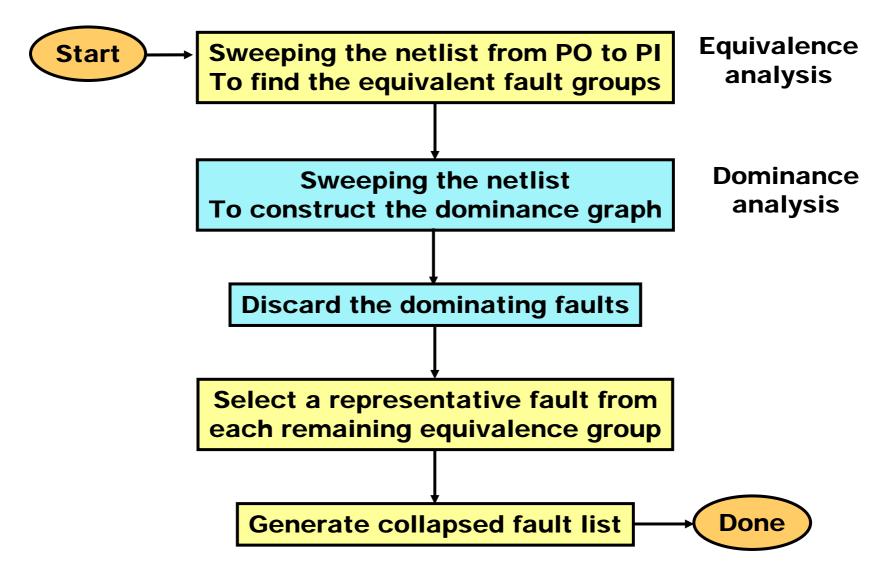

## **Equivalence Fault Collapsing**

n+2 instead of 2(n+1) faults need to be considered for n-input gates

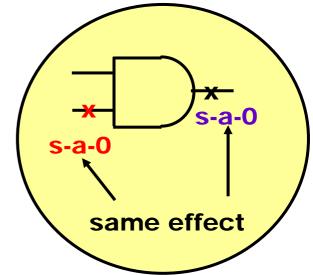

## **Equivalent Fault Group**

- In a combinational circuit

- Many faults may form an equivalent group

- These equivalent faults can be found by sweeping the circuit from the primary outputs to the primary inputs

#### Three faults shown are equivalent !

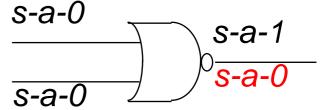

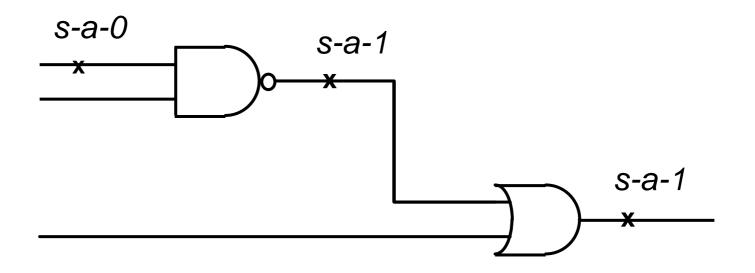

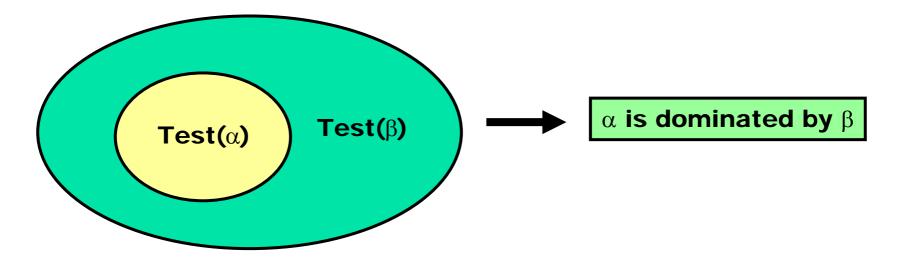

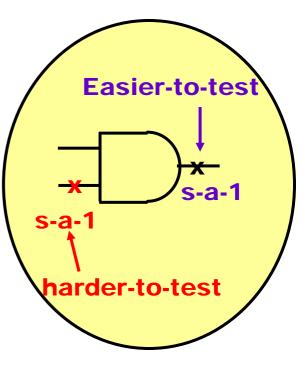

## **Fault Dominance**

- Dominance Relation

- A fault  $\beta$  is said to *dominate* another fault α in an irredundant circuit, iff every test (sequence) for α is also a test (sequence) for  $\beta$ .

- **I.e.**, test-set( $\beta$ ) > test-set( $\alpha$ )

- No need to consider fault  $\beta$  for fault detection

## **Fault Dominance**

- AND gate:

- Output *s-a-1* dominates any input *s-a-1*

- NAND gate:

- Output s-a-0 dominates any input s-a-1

- OR gate:

- Output s-a-0 dominates any input s-a-0

- NOR gate:

- Output *s-a-1* dominates any input *s-a-0*

- Dominance fault collapsing:

- The reduction of the set of faults to be analyzed based on dominance relation

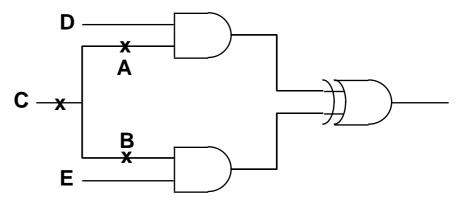

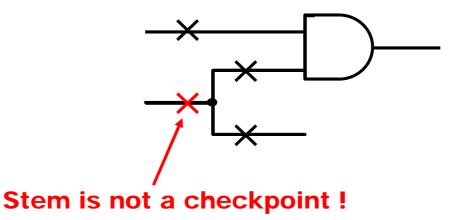

#### **Stem v.s. Branch Faults**

• Detect A sa1:

$z(t) \oplus z_f(t) = (\mathbf{CD} \oplus \mathbf{CE}) \oplus (\mathbf{D} \oplus \mathbf{CE}) = \mathbf{D} \oplus \mathbf{CD} = \mathbf{1}$

$$\Rightarrow$$

(C = 0, D = 1)

• Detect C sa1:

$$z(t) \oplus z_f(t) = (\mathbf{CD} \oplus \mathbf{CE}) \oplus (\mathbf{D} \oplus \mathbf{E}) = \mathbf{1}$$

$$\Rightarrow$$

(C=0, D=1) or (C=0, E=1)

- Hence, C sa1 dominates A sa1

- Similarly

- C sa1 dominates B sa1

- C sa0 dominates A sa0

- C sa0 dominates B sa0

- In general, there might be no equivalence or dominance relations between stem and branch faults Chang, Huang, Li, Lin, Liu

## **Analysis of a Single Gate**

| AB | С | А   | В   | C   | А   | В   | С   |

|----|---|-----|-----|-----|-----|-----|-----|

|    |   | sa1 | sa1 | sa1 | sa0 | sa0 | sa0 |

| 00 | 0 |     |     | 1   |     |     |     |

| 01 | 0 | 1   |     | 1   |     |     |     |

| 10 | 0 |     | 1   | 1   |     |     |     |

| 11 | 1 |     |     |     | 0   | 0   | 0   |

• Fault Equivalence Class

\_ (A s-a-0, B s-a-0, C s-a-0)

• Fault Dominance Relations

- (C s-a-1 > A s-a-1) and (C s-a-1 > B s-a-1)

• Faults that can be ignored:

$-\,$  A s-a-0, B s-a-0, and C s-a-1  $\,$

## **Fault Collapsing**

- Equivalence + Dominance

- For each *n*-input gate, we only need to consider *n*+1 faults during test generation

## **Dominance Graph**

- Rule

- When fault  $\alpha$  dominates fault  $\beta,$  then an arrow is pointing from  $\alpha$  to  $\beta$

- Application

- Find out the transitive dominance relations among faults

# **Fault Collapsing Flow**

## **Prime Fault**

- α is a prime fault if every fault that is dominated by α is also equivalent to α

- Representative Set of Prime Fault (RSPF)

- A set that consists of exactly one prime fault from each equivalence class of prime faults

- True minimal RSPF is difficult to find

# Why Fault Collapsing ?

- Memory and CPU-time saving

- Ease testing generation and fault simulation

\* 30 total faults  $\rightarrow$  12 prime faults

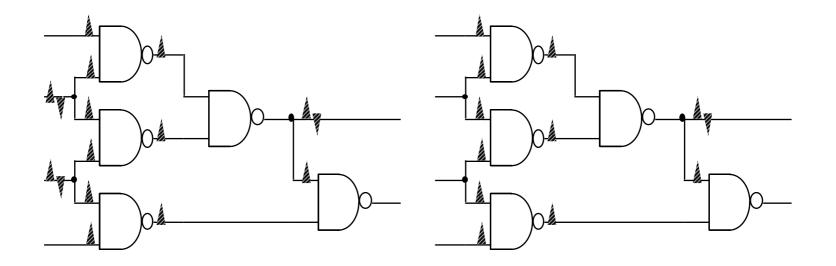

## **Checkpoint Theorem**

- Checkpoints for test generation

- A test set detects every fault on the primary inputs and fanout branches is complete

- \_ I.e., this test set detects all other faults too

- Therefore, primary inputs and fanout branches form a sufficient set of checkpoints in test generation

- In fanout-free combinational circuits, primary inputs are the checkpoints

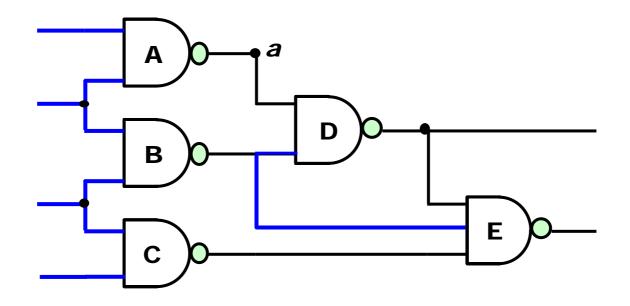

# Why Inputs + Branches Are Enough ?

- Example

- Checkpoints are marked in blue

- Sweeping the circuit from PI to PO to examine every gate, e.g., based on an order of (A->B->C->D->E)

- For each gate,

output faults are detected if every input fault is detected

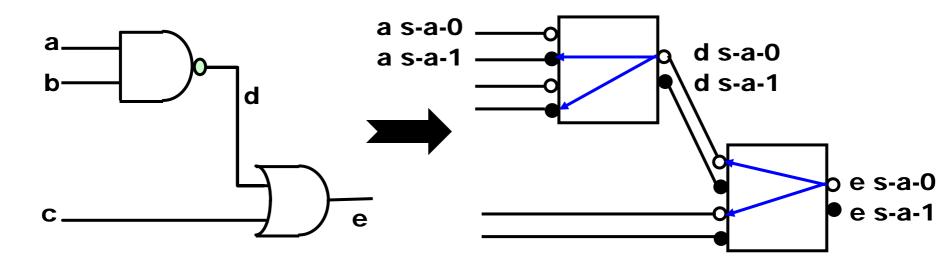

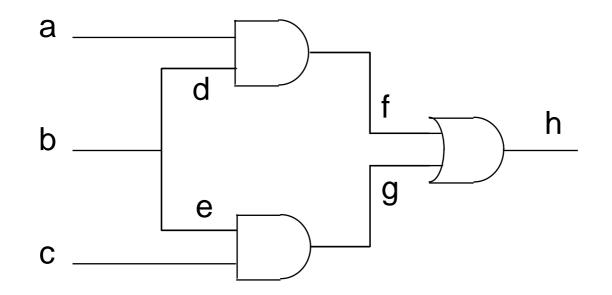

## Fault Collapsing + Checkpoint

- Example:

- 10 checkpoint faults

- a s-a-0 <=> d s-a-0 , c s-a-0 <=> e s-a-0

- bs-a-0 > ds-a-0, bs-a-1 > ds-a-1

- 6 tests are enough

Chang, Huang, Li, Lin, Liu

# Outline

- Introduction

- Fault Modeling

- Fault Simulation

- Test Generation

- Design For Testability

# Why Fault Simulation ?

- To evaluate the quality of a test set

- I.e., to compute its fault coverage

- Part of an ATPG program

- A vector usually detected multiple faults

- Fault simulation is used to compute the faults accidentally detected by a particular vector

- To construct fault-dictionary

- For post-testing diagnosis

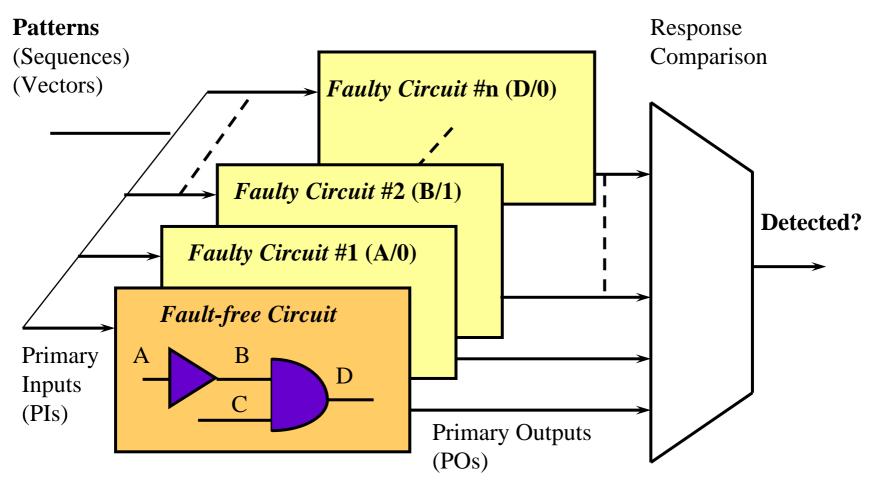

## **Conceptual Fault Simulation**

Logic simulation on both good (fault-free) and faulty circuits

## **Some Basics for Logic Simulation**

- For fault simulation purpose,

- mostly the gate delay is assumed to be zero unless the delay faults are considered. Our main concern is the functional faults

- The logic values

- can be either two (0, 1) or three values (0, 1, X)

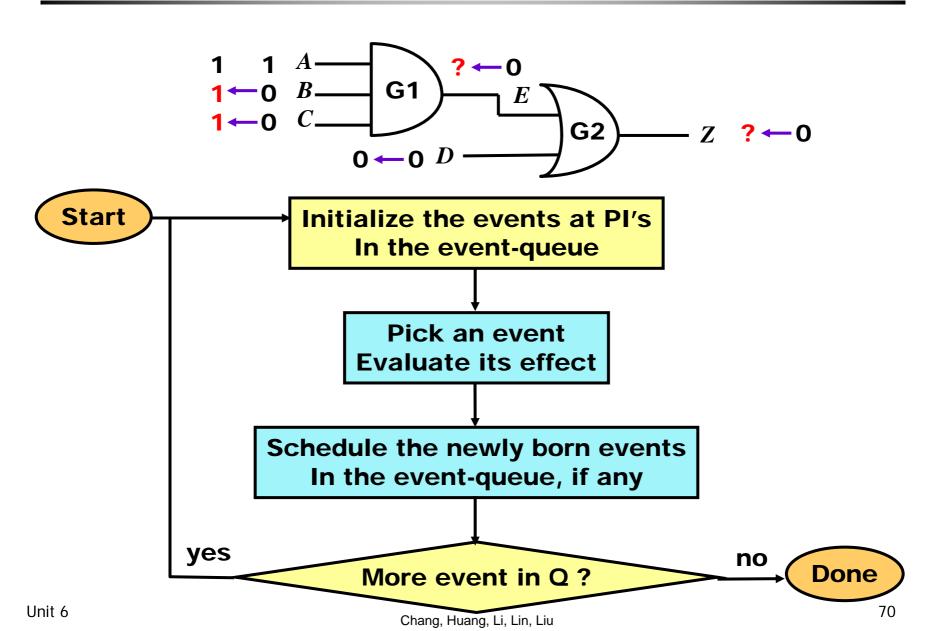

- Two simulation mechanisms:

- Oblivious compiled-code:

- circuit is translated into a program and all gates are executed for each pattern. (may have redundant computation)

- Interpretive event-driven:

- Simulating a vector is viewed as a sequence of value-change events propagating from the PI's to the PO's

- Only those logic gates affected by the events are re-evaluated

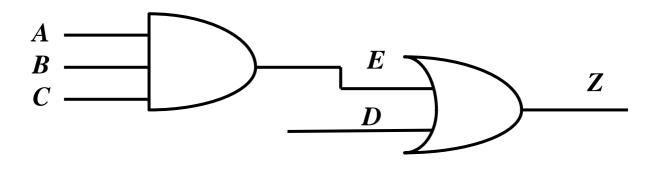

#### **Compiled-Code Simulation**

- Compiled code

- LOAD A

- AND B

- AND C

- OR *D*

- STORE Z

- /\* load accumulator with value of A \*/

- /\* calculate A and B \*/

- /\* calculate E = AB and C \*/

- /\* calculate  $Z = E \text{ or } D^*/$

- /\* store result of  $Z^*/$

#### **Event-Driven Simulation**

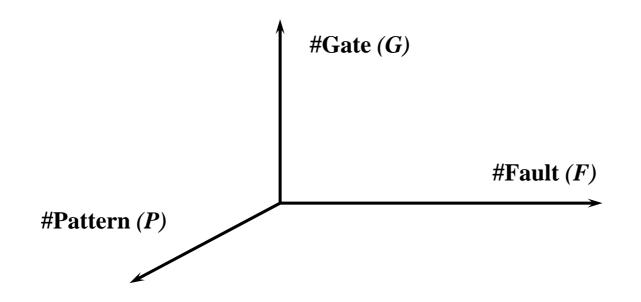

## **Complexity of Fault Simulation**

- Complexity ~  $F \cdot P \cdot G \sim O(G^3)$

- The complexity is higher than logic simulation by a factor of *F*, while usually is much lower than ATPG

- The complexity can be greatly reduced using

- Fault dropping and other advanced techniques

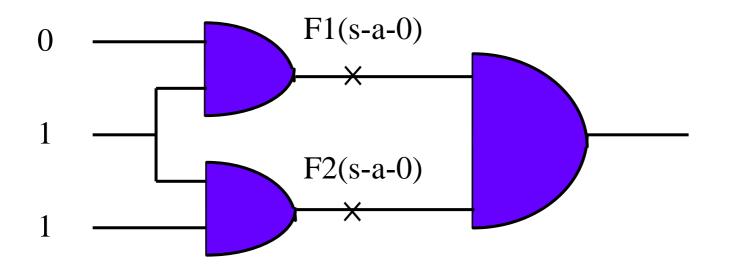

## **Characteristics of Fault Simulation**

- Fault activity with respect to fault-free circuit

- is often sparse both in time and in space.

- For example

- F1 is not activated by the given pattern, while F2 affects only the lower part of this circuit.

# **Fault Simulation Techniques**

- Serial Fault Simulation

- trivial single-fault single-pattern

- Parallel Fault Simulation

- Deductive Fault Simulation

- Concurrent Fault Simulation

# **Parallel Fault Simulation**

- Simulate multiple circuits at a time:

- The inherent parallel operation of computer words to simulate faulty circuits in parallel with fault-free circuit

- The number of faulty circuits, or faults, can be processed simultaneously is limited by the word length, e.g., 32 circuits for a 32-bit computer

- Extra Cost:

- An event, a value-change of a single fault or fault-free circuit leads to the computation of the entire word

- The fault-free logic simulation is repeated for each pass

#### **Example: Parallel Fault Simulation**

# **Deductive Fault Simulation**

- Simulate all faulty circuits in one pass

- For each pattern, sweep the circuit from PI's to PO's.

- During the process, a list of faults is associated with each line

- The list contains faults that would produce a fault effect on this line

- The union fault list at every PO contains the detected faults by the simulated input vector

- Major operation: fault list propagation

- Related to the gate types and values

- The size of the list may grow dynamically, leading to a potential memory explosion problem

# **Illustration of Fault List Propagation**

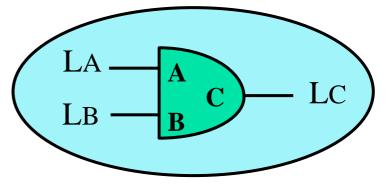

Consider a two-input AND-gate:

Non-controlling case:

**Controlling cases:**

Case 1: A=1, B=1, C=1 at fault-free, LC = LA + LB + {C/0} Case 2: A=1, B=0, C=0 at fault-free, LC = LA \* LB + {C/1} Case 3: A=0, B=0, C=0 at fault-free, LC = LA \* LB + {C/1}

#### LA is the set of all faults not in LA

# **Fault List Propagation Rule**

- Notations:

- Let *I* be the set of inputs of a gate *Z* with controlling value

*c* and inversion *i*

- (i.e., i is 0 for AND, OR and 1 for NAND, NOR)

- Let C be the set of inputs with value c

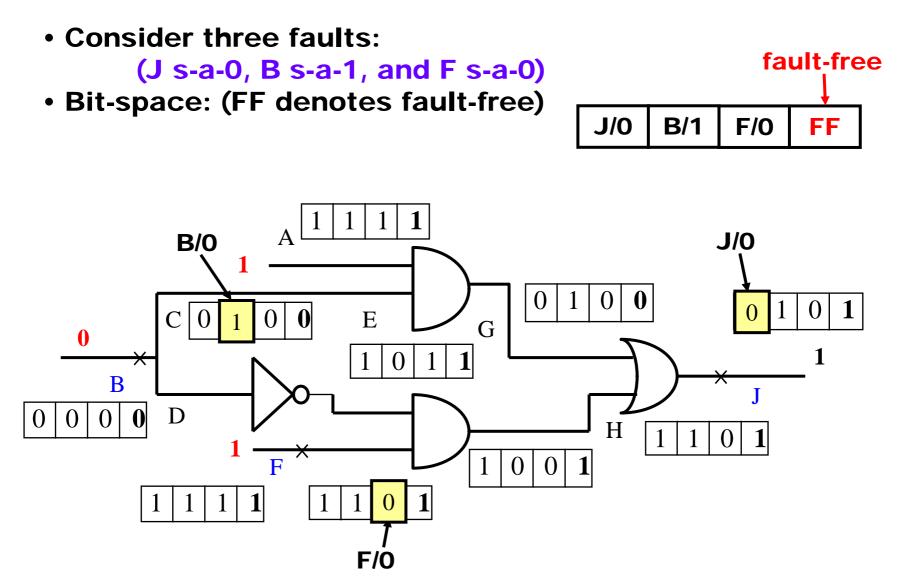

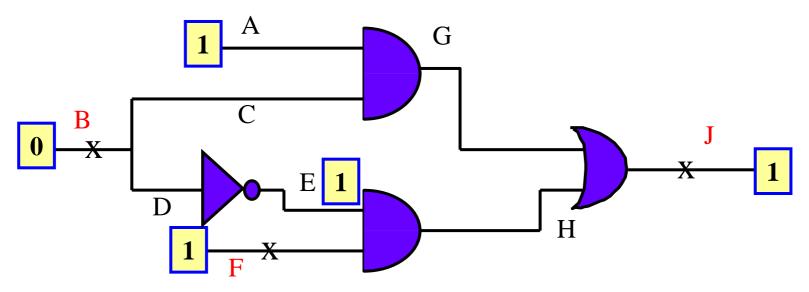

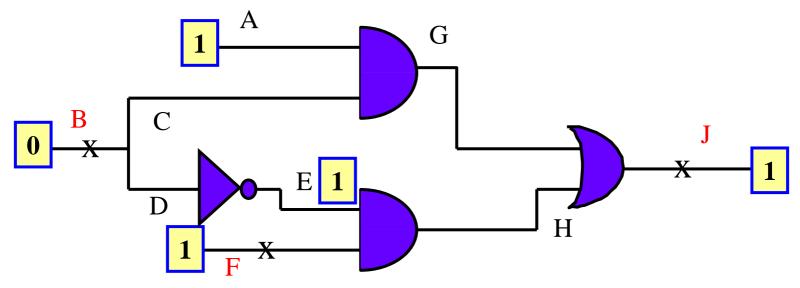

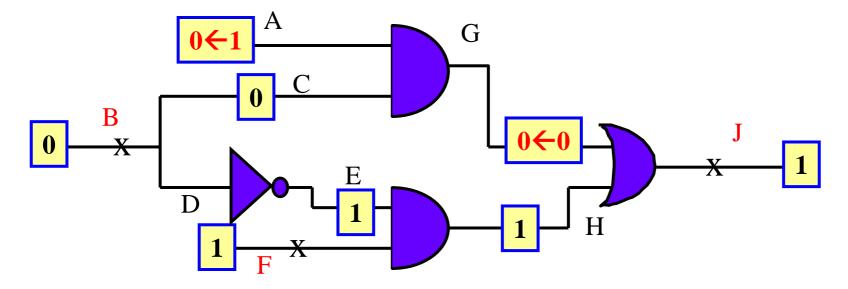

# **Example: Deductive Simulation (1)**

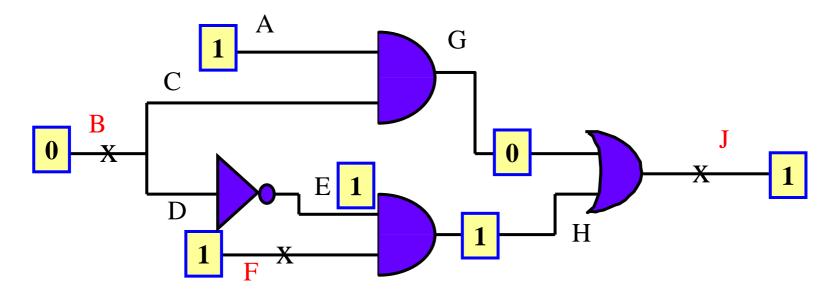

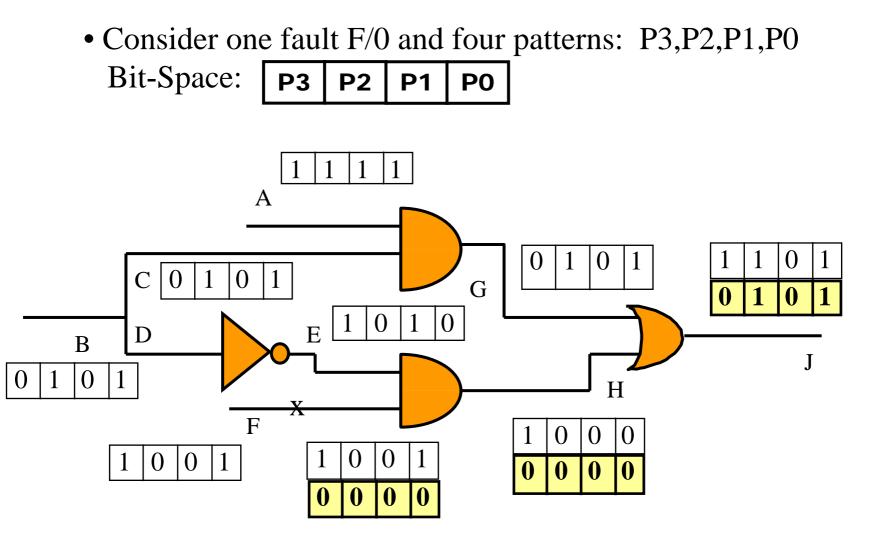

• Consider 3 faults: B/1, F/0, and J/0

Fault List at Pl's:

LB = {B/1}, LF = {F/0}, LA =  $\phi$ , LC=LD = {B/1}

# **Example: Deductive Simulation (2)**

• Consider 3 faults: B/1, F/0, and J/0

Fault Lists at G and E:

LB = {B/1}, LF = {F/0}, LA =  $\phi$ , LC=LD = {B/1}, LG = (LA \* LC) = {B/1} LE = (LD) = {B/1}

# **Example: Deductive Simulation (3)**

• Consider 3 faults: B/1, F/0, and J/0

**Computed Fault List at H:**

# **Example: Deductive Simulation (4)**

• Consider 3 faults: B/1, F/0, and J/0

Final Fault List at the output J:

LB = {B/1}, LF = {F/0}, LC=LD = {B/1}, LG = {B/1}, LE = {B/1} LH = {B/1, F/0}, LJ = {F/0,J/0}

# **Example: Deductive Simulation**

• When A changes from 1 to 0

**Event-driven operation:**

LB = {B/1}, LF = {F/0}, LA =

$$\phi$$

LC=LD = {B/1}, LG =  $\phi$ ,

LE = {B/1}, LH = {B/1,F/0}, LJ = {B/1,F/0,J/0}

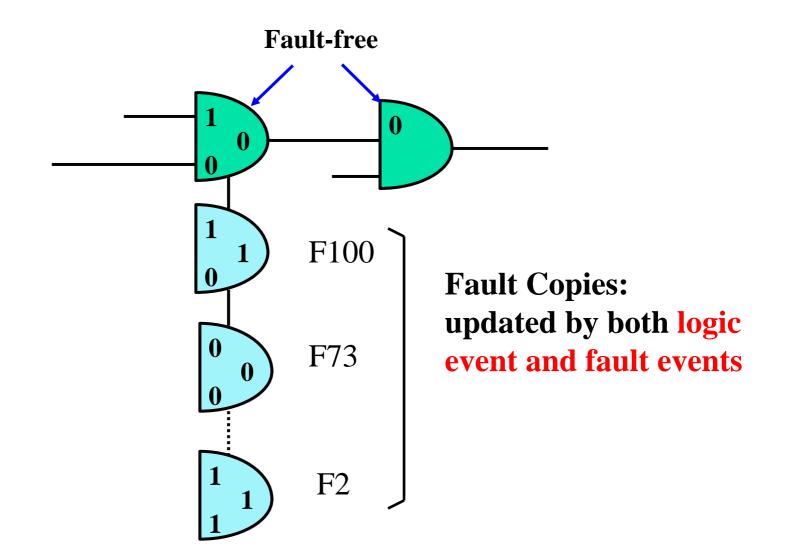

# **Concurrent Fault Simulation**

- Simulate all faulty circuits in one pass:

- Each gate retains a list of fault copies and each of them stores the status of a fault exhibiting difference from faultfree values

- Simulation mechanism

- is similar to the conceptual fault simulation except that only the dynamical difference w.r.t. fault-free circuit is retained.

- Theoretically,

- all faults in a circuit can be processed in one pass

- Practically,

- memory explosion problem may restrict the number of faults that can be processed in each pass

#### **Concurrent Fault Simulation**

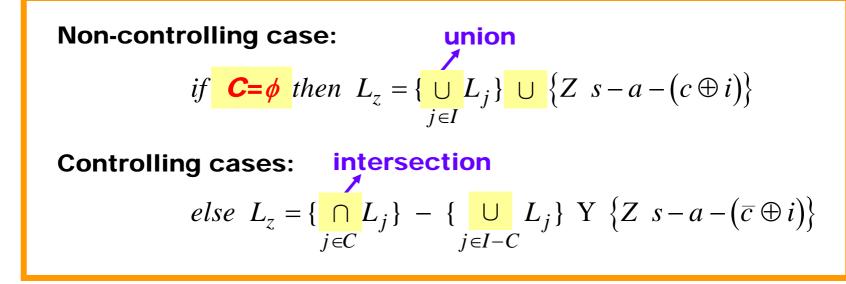

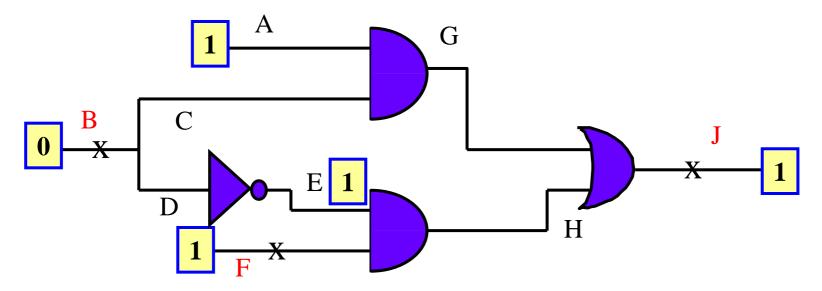

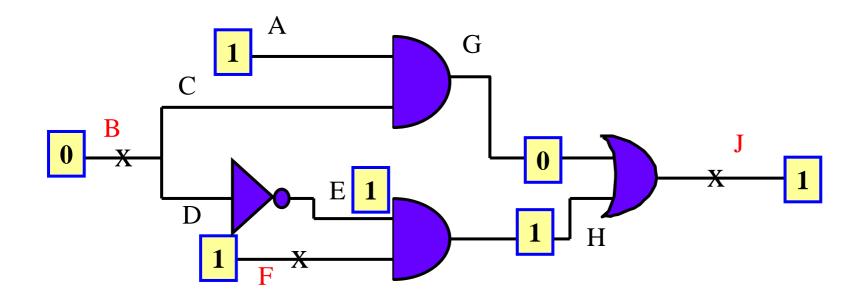

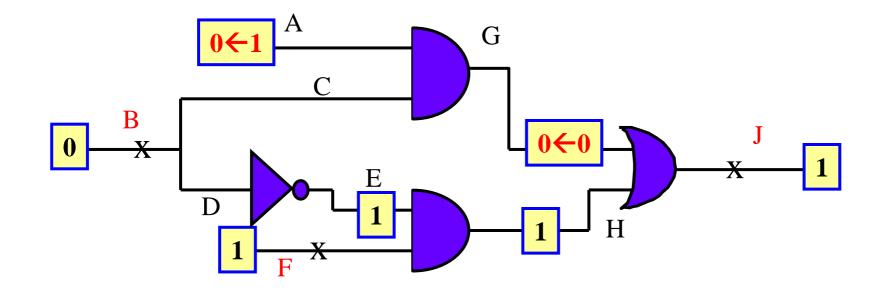

# **Example: Concurrent Simulation (1)**

• Consider 3 faults: B/1, F/0, and J/0

LG =  $\{10_0, B/1:11_1\}$  LE =  $\{0_1, B/1:1_0\}$

# **Example: Concurrent Simulation (2)**

• Consider 3 faults: B/1, F/0, and J/0

#### LG = $\{10_0, B/1:11_1\}$ LE = $\{0_1, B/1:1_0\}$ LH = $\{11_1, B/1:01_0, F/0:10_0\}$

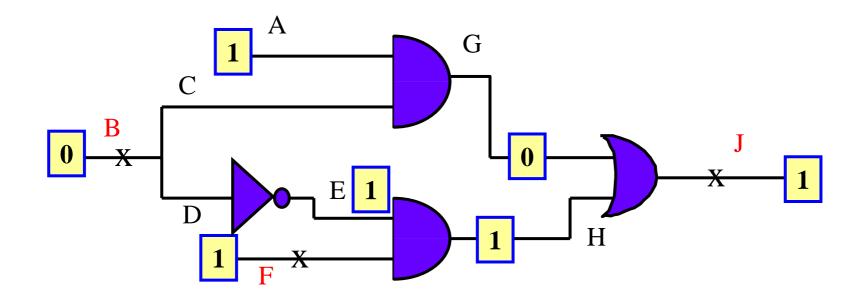

# **Example: Concurrent Simulation (3)**

• Consider 3 faults: B/1, F/0, and J/0

$LG = \{10\_0, B/1:11\_1\} LE = \{0\_1, B/1:1\_0\}$  $LH = \{11\_1, B/1:01\_0, F/0:10\_0\}$  $LJ = \{01\_1, B/1:10\_1, F/0:00\_0, J/0:01\_0\}$

# **Example: Concurrent Simulation (4)**

• When A changes from 1 to 0

LG = {00\_0, B/1:01\_0} LE = {0\_1, B/1:1\_0} LH = {11\_1, B/1:01\_0, F/0:10\_0} LJ = {01\_1, B/1:00\_0, F/0:00\_0, J/0:01\_0}

#### **Fault List of AND Gate**

Chang, Huang, Li, Lin, Liu

# **Fault List Propagation**

Chang, Huang, Li, Lin, Liu

# **Parallel-Pattern Single-Fault Simulation**

- Basic Idea:

- Event Driven + Parallel Simulation

- Parallel-Pattern Simulation

- Many patterns are simulated in parallel for both fault-free circuit and faulty circuits

- The number of patterns is a multiple of the computer wordlength

- Event-Driven

- reduction of logic event simulation time

- Simple and Extremely Efficient

- basis of most modern combinational fault simulators

# **Example: Parallel Pattern Simulation**

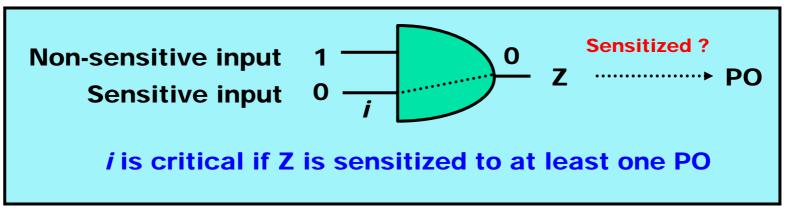

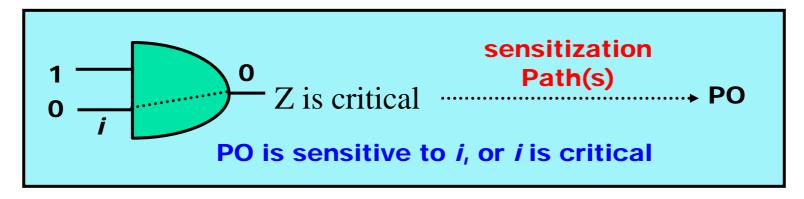

# **Sensitive Input and Critical Path**

- Sensitive Input of a gate:

- A gate input *i* is sensitive if complementing the value of *i* changes the value of the gate output

- Critical line

- Assume that the fault-free value of *w* is *v* in response to *t*

- A line w is critical w.r.t. a pattern t iff t detects the fault w stuckat v

- Critical paths

- Paths consisting of critical lines only

# **Basics of Critical Path Tracing**

- A gate input *i* is critical w.r.t. a pattern *t* if

- (1) the gate output is critical and

- (2) *i* is a sensitive input to *t*

- Use recursion to prove that *i* is also critical

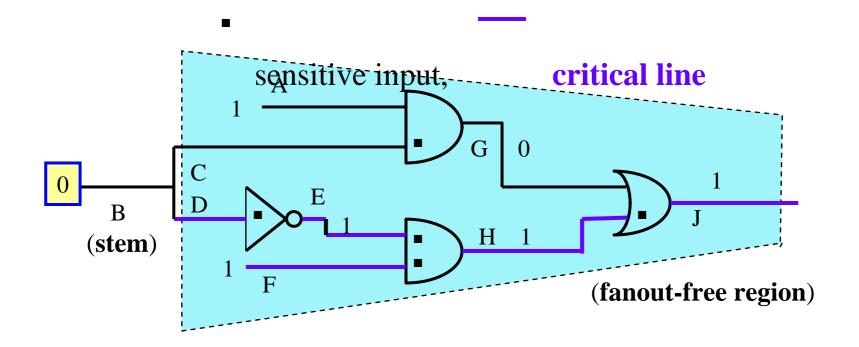

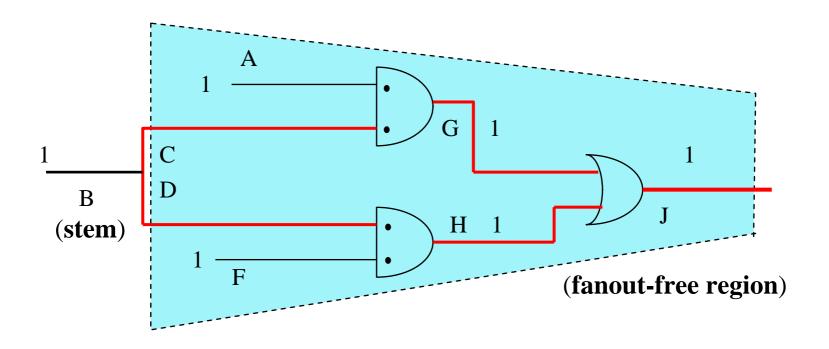

- In a fanout-free circuit

- the criticality of a line can be determined by backward traversing the sensitive gate inputs from PO's, in linear time

# **Analysis of Critical Path Tracing**

- Three-step Procedure:

- Step 1: Fault-free simulation

- Step 2: Mark the sensitive inputs of each gate

- Step 3: Identification of the critical lines by backward critical path tracing)

- Complexity is O(G)

- Where G is the gate count

- \_ for fanout-free circuits --- very rare in practice

- Application

- Applied to fanout-free regions, while stem faults are still simulated by parallel-pattern fault simulator.

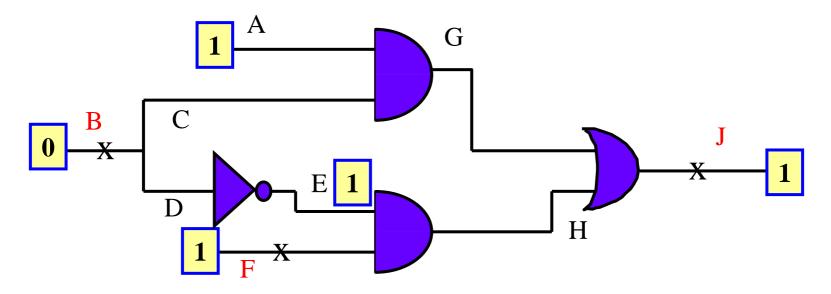

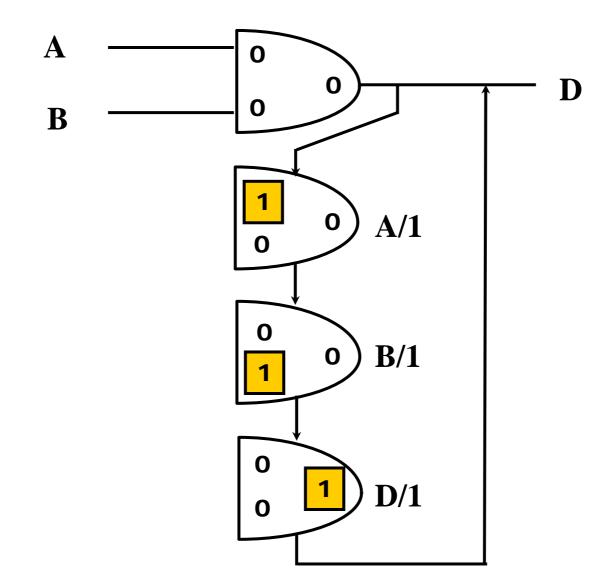

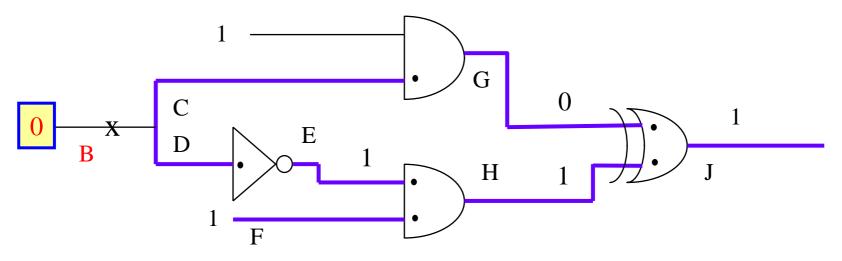

#### **Example of Critical Path Tracing**

# Detected faults in the fanout-free region: {J/0, H/0, F/0, E/0, D/1} Question: is B stuck-at-1 detected ?

# **Anomaly of Critical Path Tracing**

• **Stem criticality** is hard to infer from branches. E.g. is B/1 detectable by the given pattern?

- It turns out that **B/1 is not detectable** even though both C and D are critical, because their effects cancel out each other at gate J, (i.e., fault masking problem)

- There is also a so-called multiple path sensitization problem.

#### **Multiple Path Sensitization**

# Both C and D are not critical, yet B is critical and B/0 can be detected at J by multiple path sensitization.

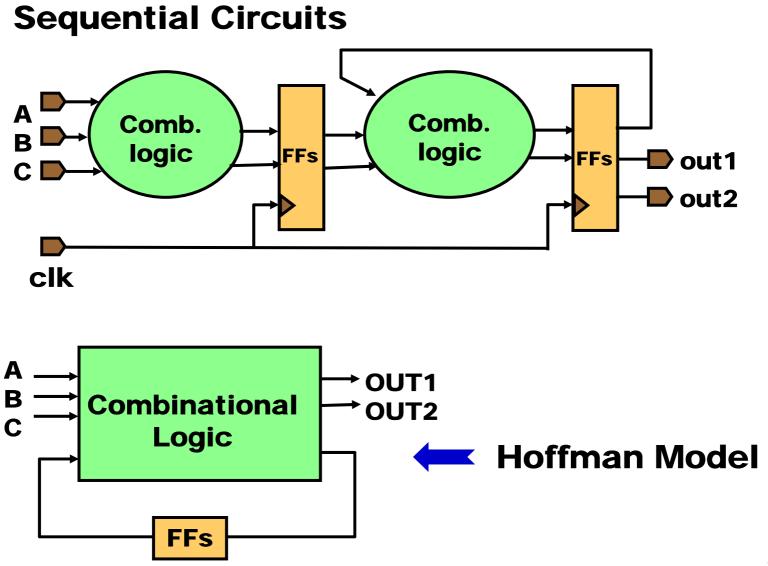

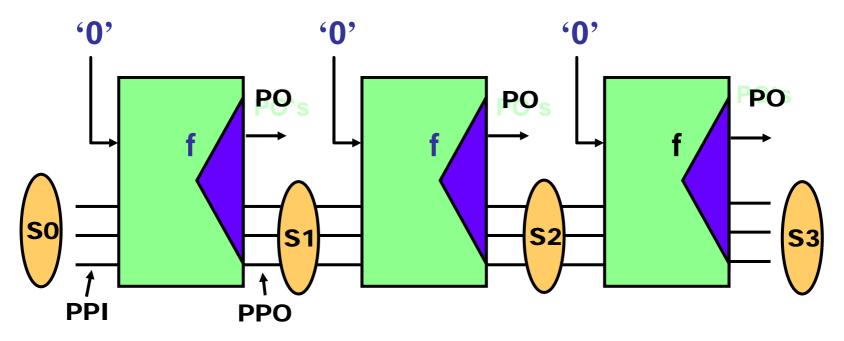

# **Sequential Fault Simulation**

- Modern Techniques:

- Fault simulation without restoration

- Parallel fault simulation

- Adoption of advanced combinational techniques

- Management of hypertrophic faults

- Other techniques:

- parallel-sequence and parallel-pattern

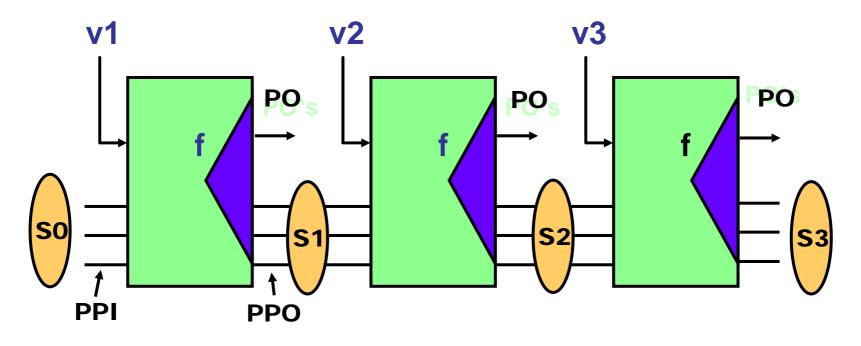

Ex: Input Sequence ('0', '0', '0') State Sequence (S0  $\rightarrow$  S1  $\rightarrow$  S2  $\rightarrow$  S3)

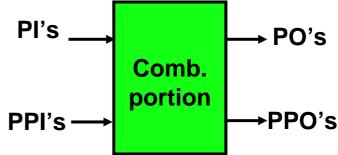

Notations: PPI: pseudo primary inputs (I.e., outputs of flip-flops) Time-frame PPO: pseudo primary outputs (I.e., inputs of flip-flops)

A single fault becomes multiple faults in the time-frame-expansion model

#### Parallel Pattern Simulation for Sequential Circuits?

Ex: Input Sequence (v1, v2, v3, ...) State Sequence (S0  $\rightarrow$  S1  $\rightarrow$  S2  $\rightarrow$  S3  $\rightarrow$  ...)

If (next-state function) depends on only k previous input vectors  $\rightarrow$ Then parallel pattern simulation would take (k+1) passes to converge !

# Outline

- Introduction

- Fault Modeling

- Fault Simulation

- Test Generation

- Design For Testability

# Outline of ATPG (Automatic Test Pattern Generation)

- Test Generation (TG) Methods

- Based on Truth Table

- Based on Boolean Equation

- Based on Structural Analysis

- D-algorithm [Roth 1967]

- 9-Valued D-algorithm [Cha 1978]

- PODEM [Goel 1981]

- FAN [Fujiwara 1983]

# **General ATPG Flow**

- ATPG (Automatic Test Pattern Generation)

- Generate a set of vectors for a set of target faults

- Basic flow

Initialize the vector set to NULL

Repeat

Generate a new test vector

**Evaluate fault coverage for the test vector**

If the test vector is acceptable, then add it to the vector set

**Until required fault coverage is obtained**

- To accelerate the ATPG

- Random patterns are often generated first to detect easy-todetect faults, then a deterministic TG is performed to generate tests for the remaining faults

# **Combinational ATPG**

- Test Generation (TG) Methods

- Based on Truth Table

- Based on Boolean Equation

- Based on Structural Analysis

- Milestone Structural ATPG Algorithms

- D-algorithm [Roth 1967]

- 9-Valued D-algorithm [Cha 1978]

- PODEM [Goel 1981]

- FAN [Fujiwara 1983]

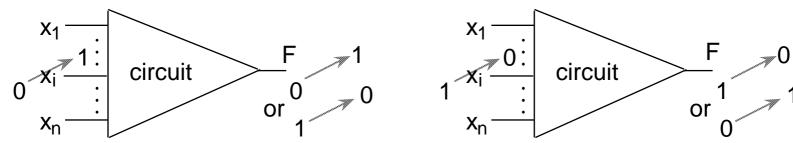

A Fully Specified Test Pattern (every PI is either 0 or 1)

A Partially Specified Test Pattern (certain Pl's could be undefined)

Chang, Huang, Li, Lin, Liu

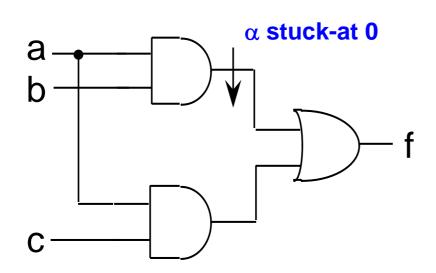

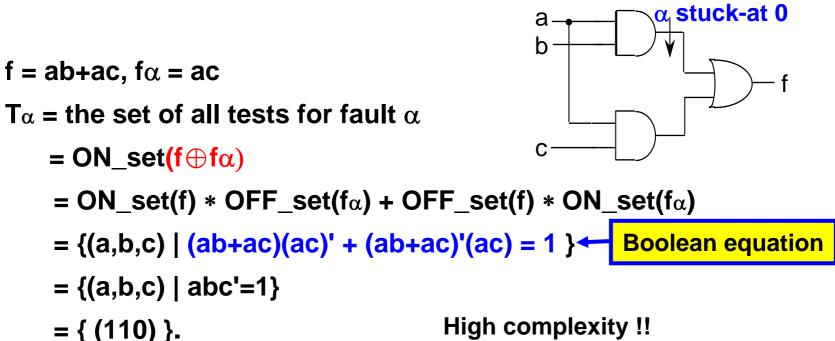

#### Test Generation Methods (From Truth Table)

#### Ex: How to generate tests for the stuck-at 0 fault (fault α)?

| abc | f | fα |

|-----|---|----|

| 000 | 0 | 0  |

| 001 | 0 | 0  |

| 010 | 0 | 0  |

| 011 | 0 | 0  |

| 100 | 0 | 0  |

| 101 | 1 | 1  |

| 110 | 1 | 0  |

| 111 | 1 | 1  |

## **Test Generation Methods**

(Using Boolean Equation)

High complexity !! Since it needs to compute the faulty function for each fault.

\* ON\_set(f): All input combinations to which f evaluates to 1.

OFF\_set(f): All input combinations to which f evaluates to 0.

Note: a function is characterized by its ON\_SET

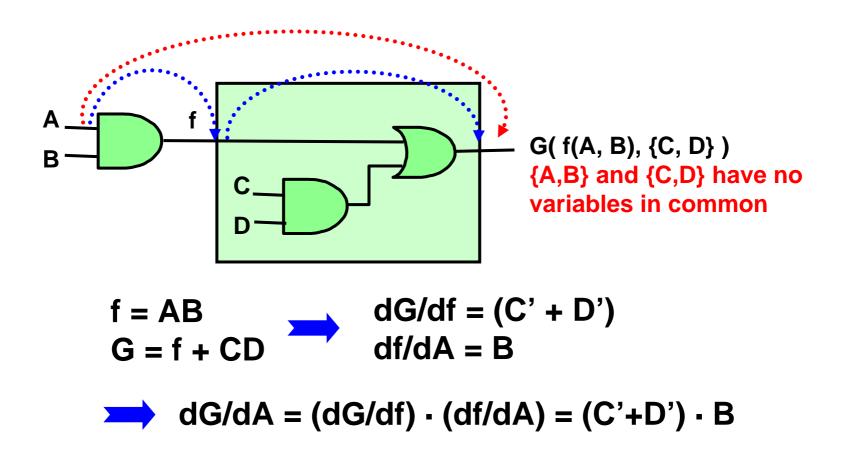

## **Boolean Difference**

- Physical Meaning of Boolean Difference

- For a logic function F(X)=F(x1, ..., xi, ..., xn), find all the input combinations that make a value-change at xi also cause a valuechange at F.

- Logic Operation of Boolean Difference

- The Boolean difference of F(X) w.r.t. input xi is

$\frac{dF(x)}{dx_{i}} = F_{i}(0) \oplus F_{i}(1) = F_{i}(0) \cdot F_{i}(1)' + F_{i}(0)' \cdot F_{i}(1)$ Where  $F_{i}(0) = F(x_{1}, ..., 0, ..., x_{n})$   $F_{i}(1) = F(x_{1}, ..., 1, ..., x_{n})$

Illustrations of Boolean Difference

## **Chain Rule**

An Input vector v sensitizes a fault effect from A to G Iff v sensitizes the effect from A to f and from f to G

## **Boolean Difference (con't)**

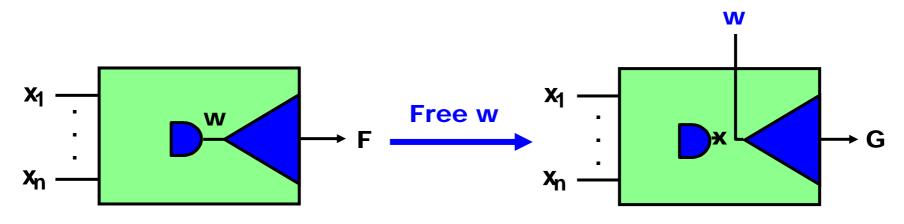

#### Boolean Difference

- With respect to an internal signal, w, Boolean difference represents the set of input combinations that sensitize a fault effect from w to the primary output F

- Calculation

- Step 1: convert the function F into a new one G that takes the signal w as an extra primary input

- Step 2:

$$dF(x_1, ..., x_n)/dw = dG(x_1, ..., x_n, w)/dw$$

## **Test Gen. By Boolean Difference**

#### **Case 1: Faults are present at PIs.**

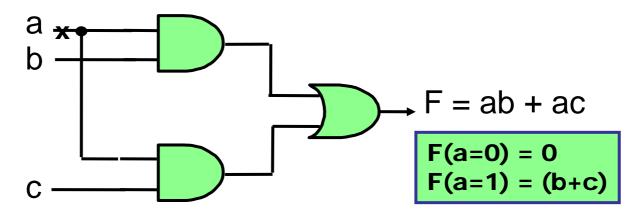

Fault Sensitization Requirement: dF/da = F(a=0) ⊕ F(a=1) = 0 ⊕ (b+c) = (b+c)

Test-set for  $a = \{(a,b,c) | a' \cdot (b+c)=1\} = \{(01x), (0x1)\}$ . Test-set for  $a = \{(a,b,c) | a \cdot (b+c)=1\} = \{(11x), (1x1)\}$ .

No need to compute The faulty function !!

Fault activation requirement

Fault sensitization requirement

## **Test Generation By Boolean Difference (con't)**

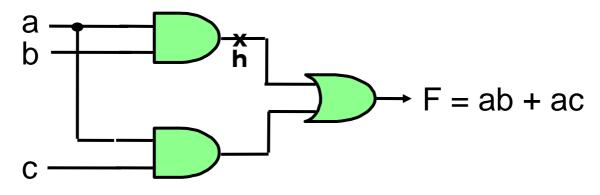

Case 2: Faults are present at internal lines.

G(i.e., F with h floating) = h + ac

dG/dh = G(h=0)

$$\oplus$$

G(h=1) = (ac  $\oplus$  1) = (a'+c')

Test-set for *h* s-a-1 is { (a,b,c)| h' • (a'+c')=1 } = { (a,b,c)| (a'+b') • (a'+c')=1 } = { (0xx), (x00) }. Test-set for *h* s-a-0 is {(a,b,c)| h • (a'+c')=1} = {(110)}. For fault activation For fault sensitization

## Outline of ATPG (Automatic Test Pattern Generation)

- Test Generation (TG) Methods

- Based on Truth Table

- Based on Boolean Equation

- Based on Structural Analysis

- D-algorithm [Roth 1967]

- 9-Valued D-algorithm [Cha 1978]

- PODEM [Goel 1981]

- FAN [Fujiwara 1983]

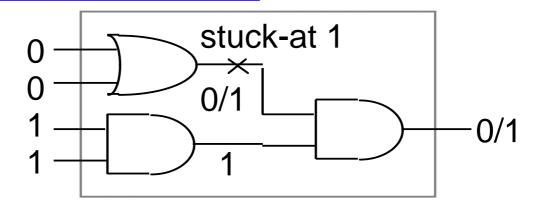

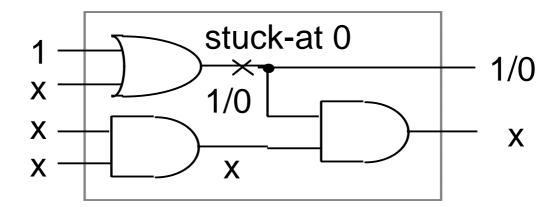

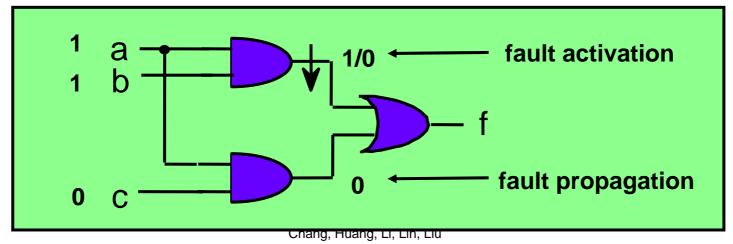

### Test Generation Method (From Circuit Structure)

- Two basic goals

- (1) Fault activation (FA)

- (2) Fault propagation (FP)

- Both of which requires Line Justification (LJ), I.e., finding input combinations that force certain signals to their desired values

- Notations:

Unit 6

- 1/0 is denoted as D, meaning that good-value is 1 while faulty value is 0

- Similarly, 0/1 is denoted D'

- Both D and D' are called fault effects (FE)

# **Common Concepts for Structural TG**

- Fault activation

- Setting the faulty signal to either 0 or 1 is a Line Justification problem

- Fault propagation

- (1) select a path to a PO  $\rightarrow$  decisions

- (2) Once the path is selected → a set of line justification (LJ) problems are to be solved

- Line Justification

- Involves decisions or implications

- Incorrect decisions: need backtracking

To justify  $c=1 \rightarrow a=1$  and b=1 (implication) To justify  $c=0 \rightarrow a=0$  or b=0 (decision)

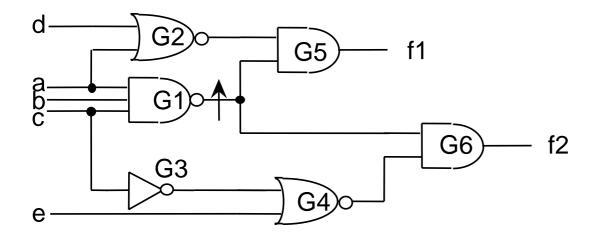

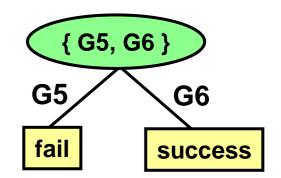

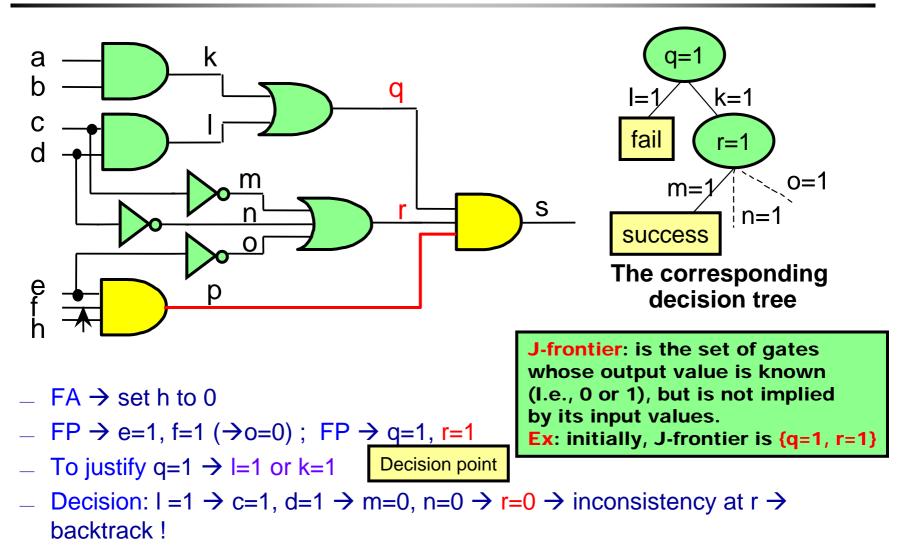

## **Ex: Decision on Fault Propagation**

decision tree

- Fault activation

- G1=0 → { a=1, b=1, c=1 } → { G3=0 }

- Fault propagation: through G5 or G6

- Decision through G5:

- G2=1  $\rightarrow$  { d=0, a=0 }  $\rightarrow$  inconsistency at a  $\rightarrow$  backtrack !!

- Decision through G6:

- $\rightarrow$  G4=1  $\rightarrow$  e=0  $\rightarrow$  done !! The resulting test is (111x0)

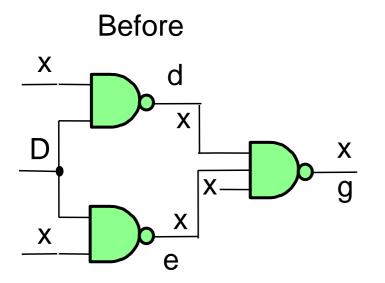

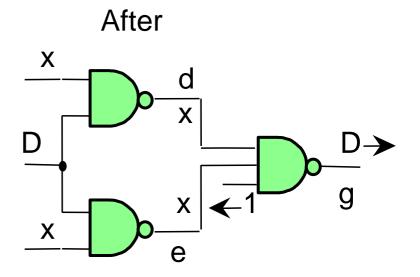

**D-frontiers**: are the gates whose output value is x, while one or more Inputs are D or D'. For example, initially, the D-frontier is { G5, G6 }.

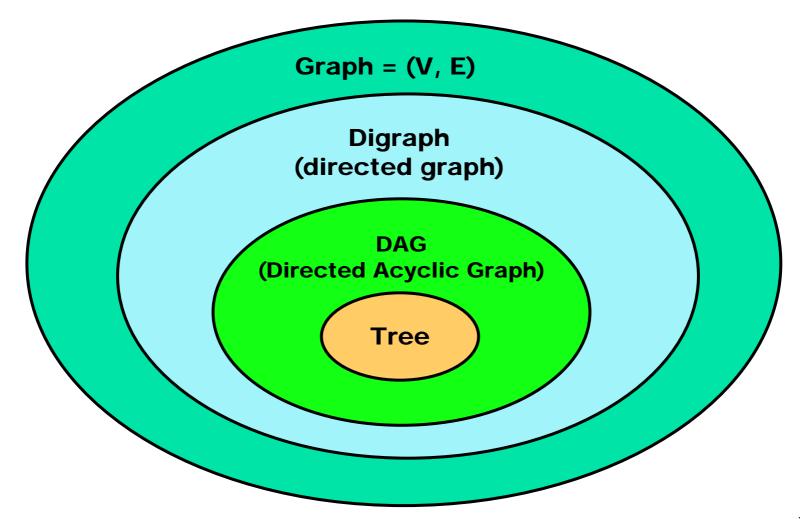

### **Various Graphs**

A Combinational Circuit: is usually modeled as a DAG, but not tree

## **Ex: Decisions On Line Justification**

Chang, Huang, Li, Lin, Liu

To justify  $r=1 \rightarrow m=1$  or  $n=1 (\rightarrow c=0 \text{ or } d=0) \rightarrow Done ! (J-frontier is <math>\phi$ )

- Decision: k=1  $\rightarrow$  a=1, b=1

Unit 6

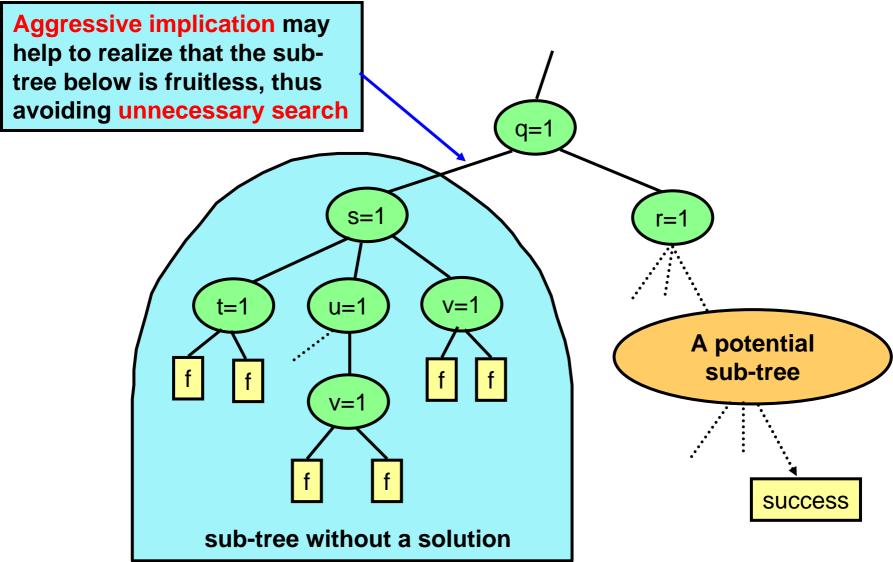

### **Branch-and-Bound Search**

- Test Generation

- Is a branch-and-bound search

- Every decision point is a branching point

- If a set of decisions lead to a conflict (or bound), a backtrack is taken to explore other decisions

- A test is found when

- (1) fault effect is propagated to a PO

- (2) all internal lines are justified

- No test is found after all possible decisions are tried → Then, target fault is undetectable

- Since the search is exhaustive, it will find a test if one exists

For a combinational circuit, an undetectable fault is also a redundant fault  $\rightarrow$  Can be used to simplify circuit.

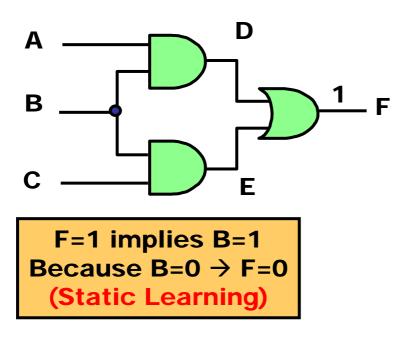

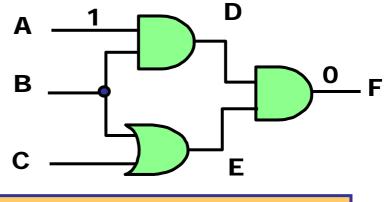

# Implications

#### • Implications

- Computation of the values that can be uniquely determined

- Local implication: propagation of values from one line to its immediate successors or predecessors

- Global implication: the propagation involving a larger area of the circuit and re-convergent fanout

- Maximum Implication Principle

- Perform as many implications as possible

- It helps to either reduce the number of problems that need decisions or to reach an inconsistency sooner

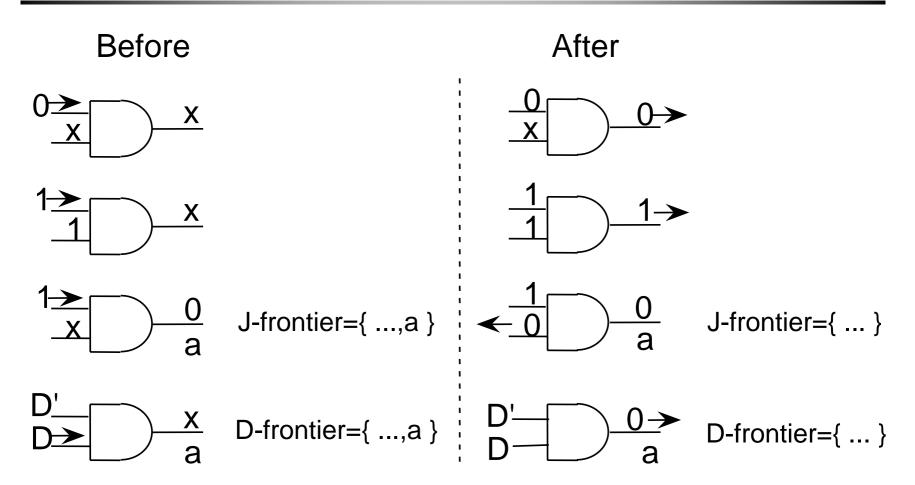

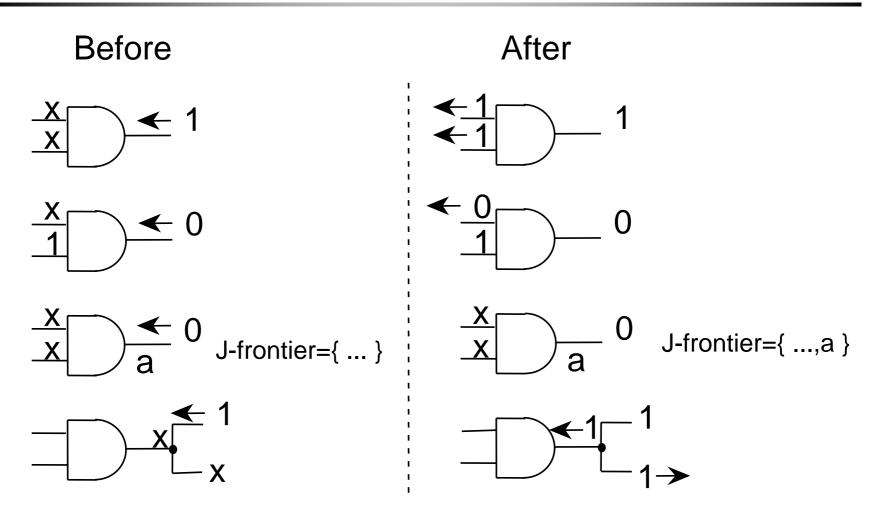

## **Local Implications (Forward)**

## **Local Implications (Backward)**

# **Global Implications**

- Unique D-Drive Implication

- Suppose D-frontier (or D-drive) is {d, e}, → g is a dominator for both d and e, hence a unique D-drive is at g

g is called a dominator of d: because every path from d to an PO passes through g

## **Learning for Global Implication**

• Static Learning

- Global implication derived by contraposition law

- Learn static (I.e., input independent) signal implications

- Dynamic Learning

- Contraposition law + other signal values

- Is input pattern dependent

F=0 implies B=0 When A=1 Because {B=1, A=1} → F=1 (Dynamic Learning)

## **Early Detection of Inconsistency**

# Ex: D-Algorithm (1/3)

Chang, Huang, Li, Lin, Liu

# Ex: D-Algorithm (3/3)

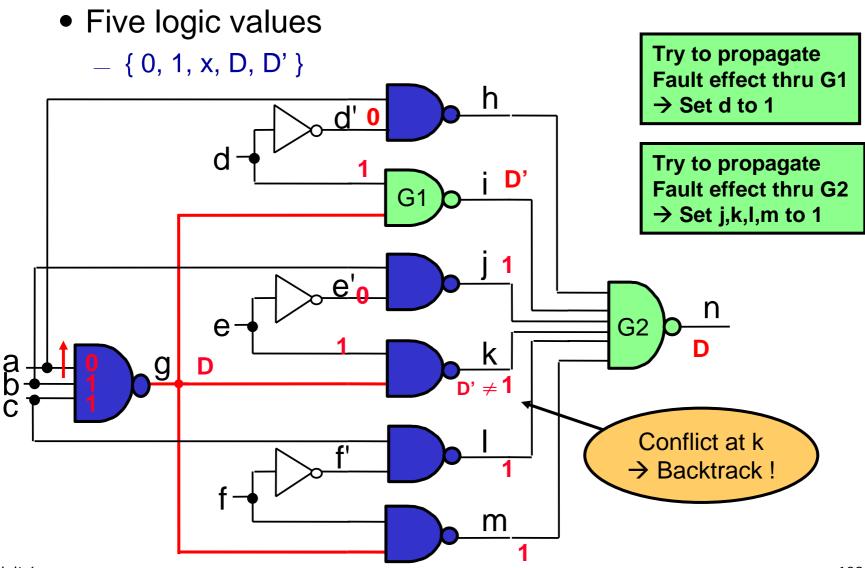

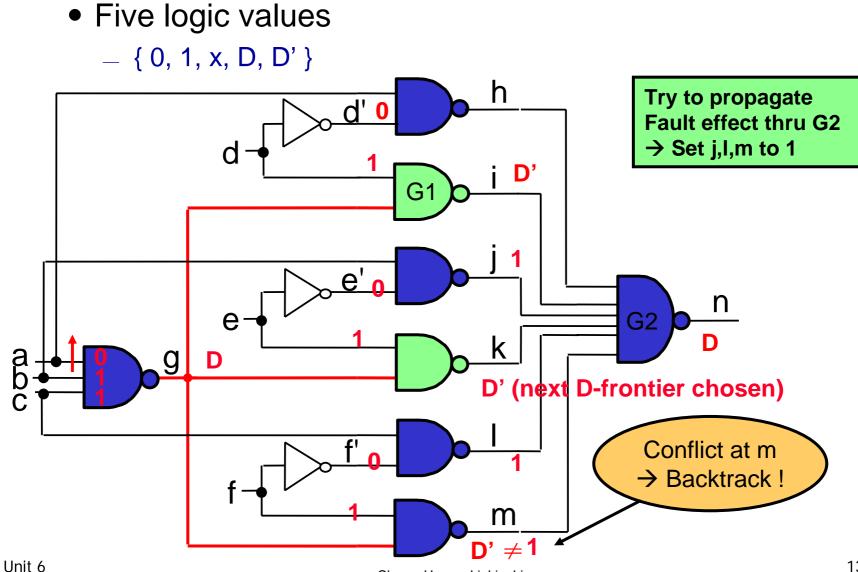

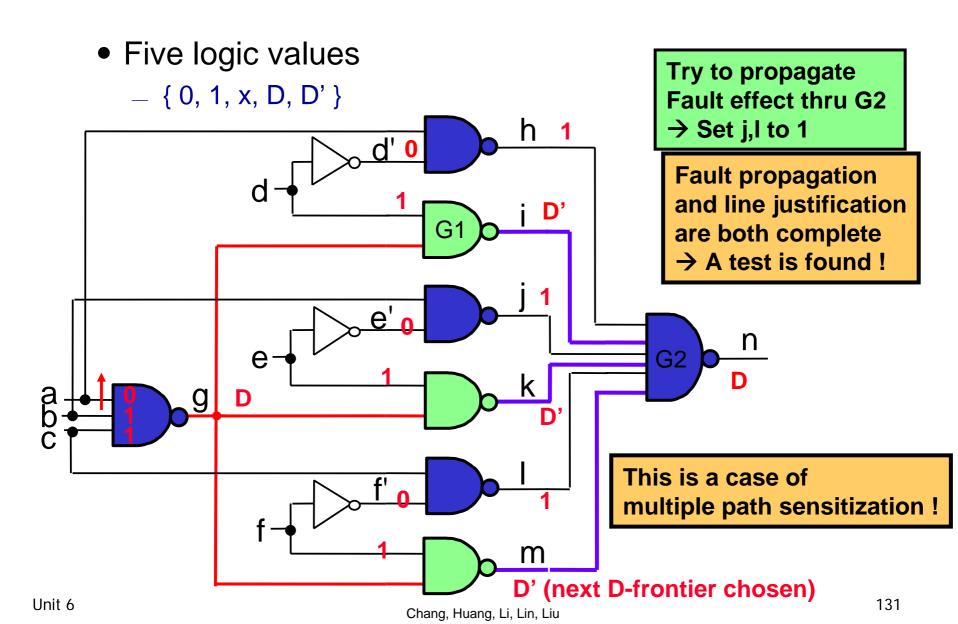

# **D-Algorithm: Value Computation**

| Decision          | Implication        | Comments                           | I          | 1                          | 1               |

|-------------------|--------------------|------------------------------------|------------|----------------------------|-----------------|

|                   | a=0<br>h=1<br>b=1  | Active the fault<br>Unique D-drive | e=1        | k=D'<br>e'=0<br>j=1        | Propagate via k |

|                   | c=1<br>g=D         |                                    | l=1<br>m=1 |                            | Propagate via n |

| d=1               | i=D'<br>d'=0       | Propagate via i                    | 111-1      | n=D<br>f'=0<br>f=1         |                 |

| j=1               |                    | Propagate via n                    |            | m=D'                       | Contradiction   |

| k=1<br>l=1<br>m=1 | n=D<br>e'=0<br>e=1 |                                    | f=1        | m=D'<br>f'=0<br>l=1<br>n=D | Propagate via m |

|                   | k=D'               | Contradiction                      |            |                            |                 |

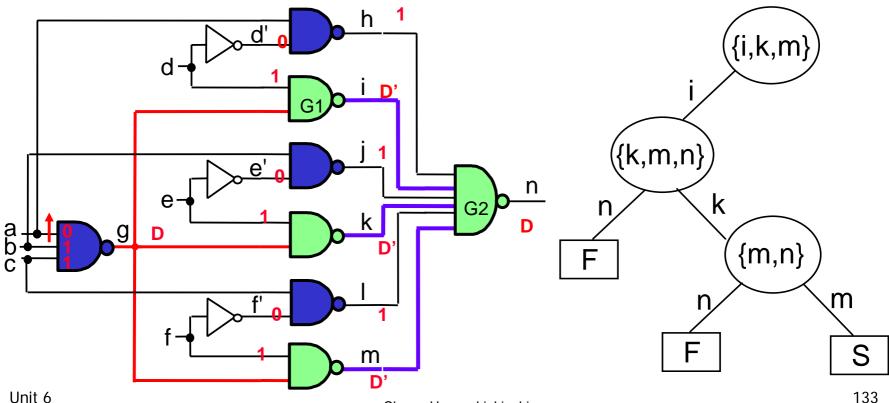

## **Decision Tree on D-Frontier**

- The decision tree below

- Node  $\rightarrow$  D-frontier

- Branch  $\rightarrow$  Decision Taken

- A Depth-First-Search (DFS) strategy is often used

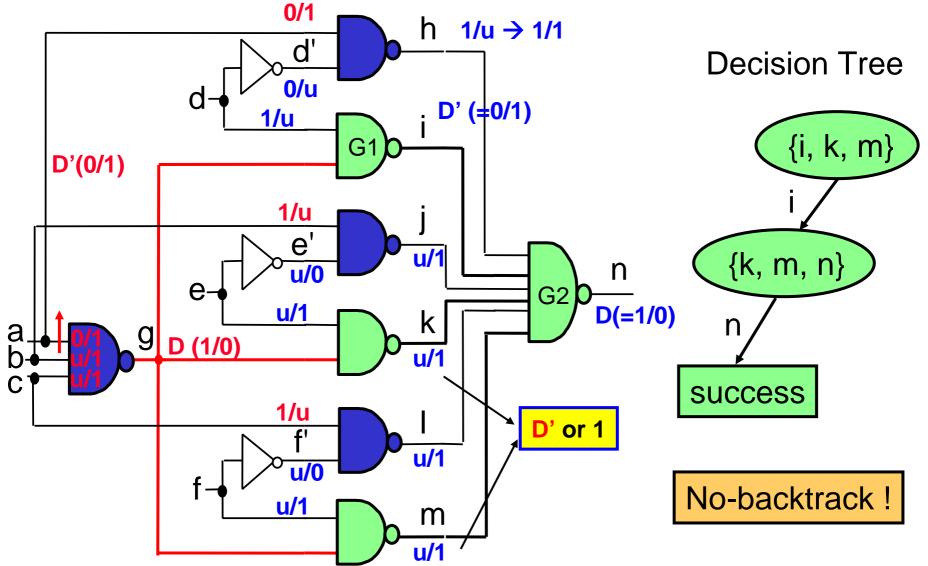

## 9-Value D-Algorithm

- Logic values (fault-free / faulty)

- {0/0, 0/1, 0/u, 1/0, 1/1, 1/u, u/0, u/1, u/u},

- where 0/u={0,D'}, 1/u={D,1}, u/0={0,D}, u/1={D',1}, u/u={0,1,D,D'}.

- Advantage:

- Automatically considers multiple-path sensitization, thus reducing the amount of search in D-algorithm

- The speed-up is NOT very significant in practice because most faults are detected through singlepath sensitization

### **Example: 9-Value D-Algorithm**

## **Final Step of 9-Value D-Algorithm**

- To derive the test vector

- $A = (0/1) \rightarrow 0$  (take the fault-free one)

- $B = (1/u) \rightarrow 1$

- $C = (1/u) \rightarrow 1$

- $D = (u/1) \rightarrow 1$

- $E = (u/1) \rightarrow 1$

- $F = (u/1) \rightarrow 1$

- The final vector

- (A,B,C,D,E,F) = (0, 1, 1, 1, 1, 1)

## Outline of ATPG (Automatic Test Pattern Generation)

- Test Generation (TG) Methods

- Based on Truth Table

- Based on Boolean Equation

- Based on Structural Analysis

- D-algorithm [Roth 1967]

- 9-Valued D-algorithm [Cha 1978]

- PODEM [Goel 1981]

- FAN [Fujiwara 1983]

## **PODEM: Path-Oriented DEcision Making**

- Fault Activation (FA) and Propagation (FP)

- lead to sets of Line Justification (LJ) problems. The LJ problems can be solved via value assignments.

- In D-algorithm

- TG is done through indirect signal assignment for FA, FP, and LJ, that eventually maps into assignments at PI's

- The decision points are at internal lines

- The worst-case number of backtracks is exponential in terms of the number of decision points (e.g., at least 2<sup>k</sup> for k decision nodes)

- In PODEM

- The test generation is done through a sequence of direct assignments at PI's

- Decision points are at PIs, thus the number of backtracking might be fewer

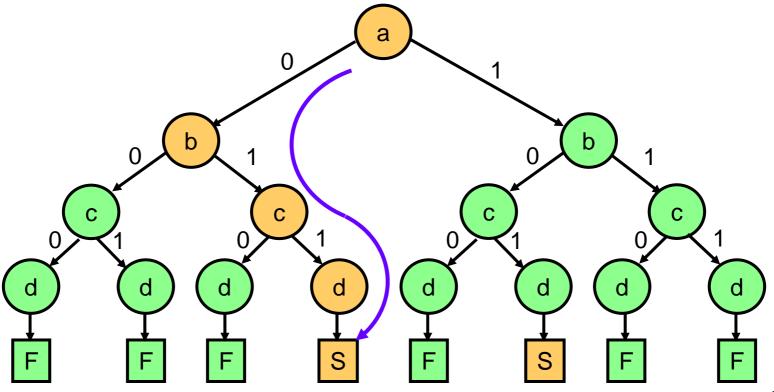

## **Search Space of PODEM**

- Complete Search Space

- A binary tree with 2<sup>n</sup> leaf nodes, where n is the number of PI's

- Fast Test Generation

- Need to find a path leading to a SUCCESS terminal quickly

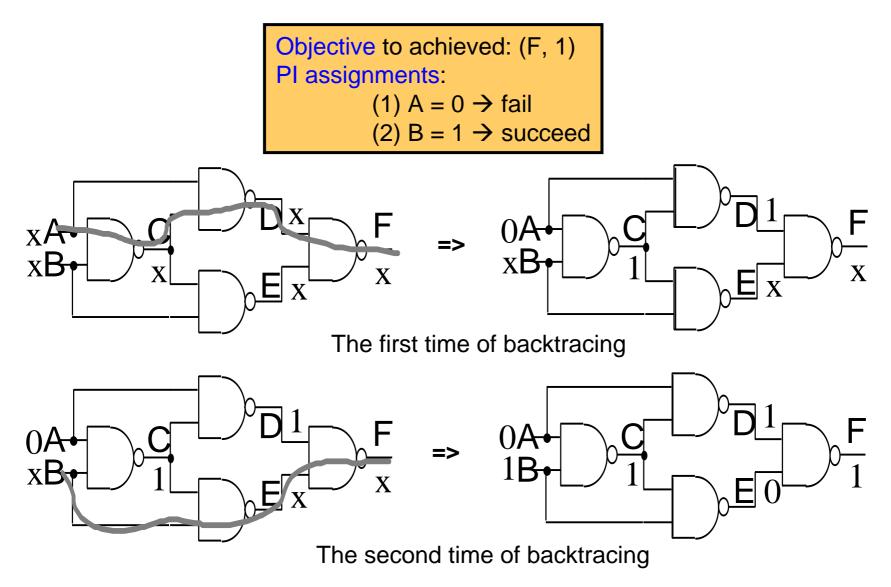

# **Objective() and Backtrace()**

- PODEM

- Also aims at establishing a sensitization path based on fault activation and propagation like D-algorithm

- Instead of justifying the signal values required for sensitizing the selected path, objectives are setup to guide the decision process at PI's

- Objective

- is a signal-value pair (w, v<sub>w</sub>)

- Backtrace

- Backtrace maps a desired objective into a PI assignment that is likely to contribute to the achievement of the objective

- Is a process that traverses the circuit back from the objective signal to PI's

- The result is a PI signal-value pair (x, v<sub>x</sub>)

- No signal value is actually assigned during backtrace 往輸入端追踪

## **Objective Routine**

#### Objective Routine Involves

- The selection of a D-frontier, G

- The selection of an unspecified input gate of G

```

Objective() {

/* The target fault is w s-a-v */

/* Let variable obj be a signal-value pair */

if (the value of w is x) obj = (w, v'); \leftarrow fault activation

else {

select an input (j) of G with value x;

c = controlling value of G;

obj = (j, c');

return (obj);

```

### **Backtrace Routine**

- Backtrace Routine

- Involves finding an all-x path from objective site to a PI, I.e., every signal in this path has value x

```

Backtrace(w, v<sub>w</sub>) {

/* Maps objective into a PI assignment */

G = w; /* objective node */

v = v_w; /* objective value */

while (G is a gate output) { /* not reached PI yet */

inv = inversion of G;

select an input (j) of G with value x;

G = j; /* new objective node */

v = v \oplus inv; /* new objective value */

/* G is a PI */ return (G, v);

```

### **Example: Backtrace**

Assume that: PI's: { a, b, c, d } Current Assignments: { a=0 } Decision: b=0  $\rightarrow$  objective fails Reverse decision: b=1 Decision: c=0  $\rightarrow$  objective fails Reverse decision: c=1 Decision: d=0

Failure means fault effect cannot be propagated to any PO under current PI assignments

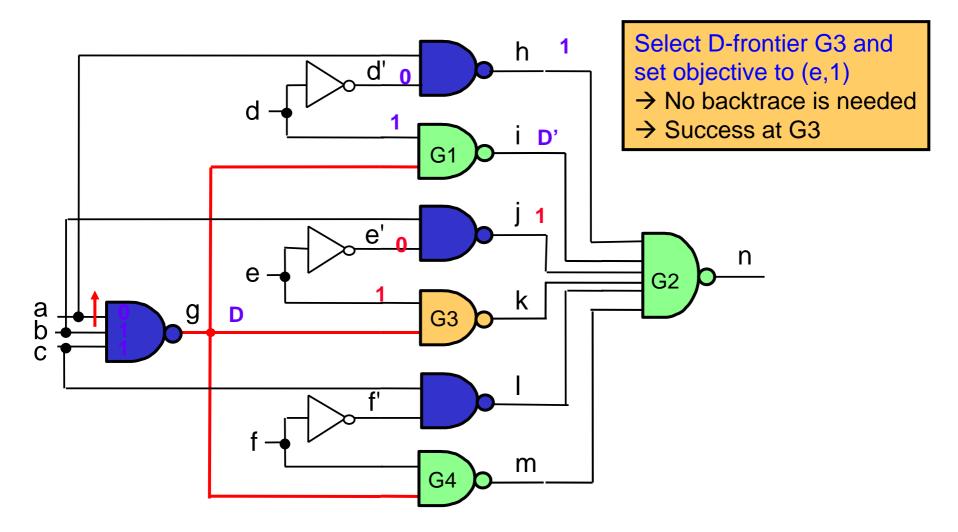

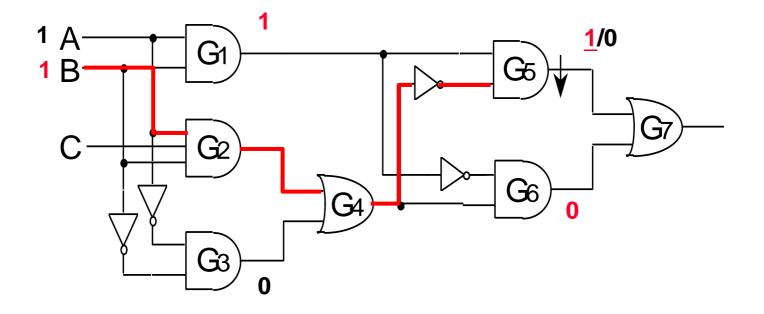

# Example: PODEM (1/3)

# Example: PODEM (2/3)

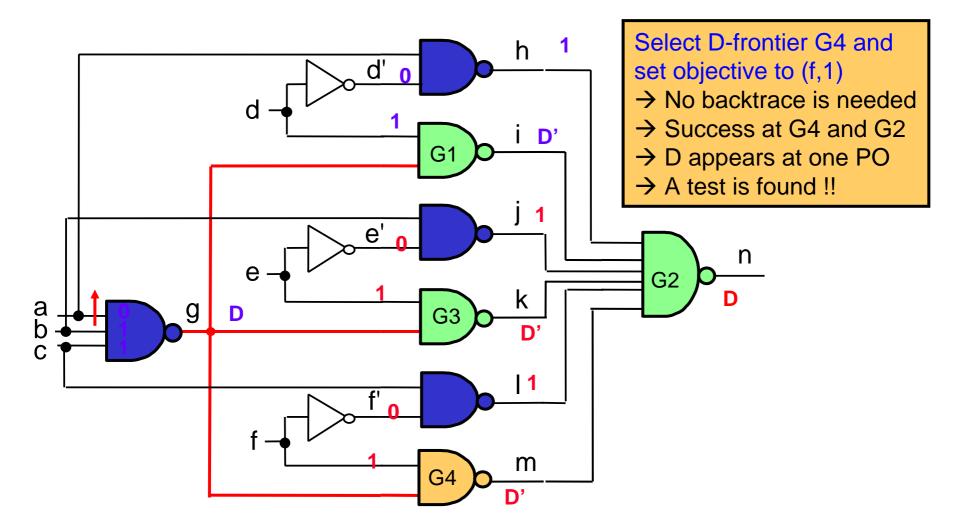

# Example: PODEM (3/3)

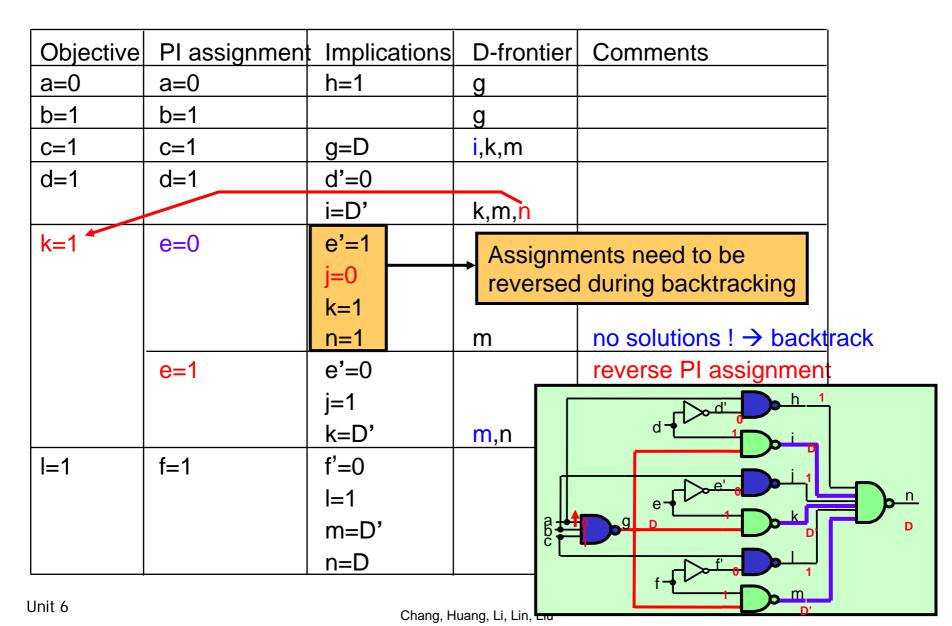

# **PODEM: Value Computation**

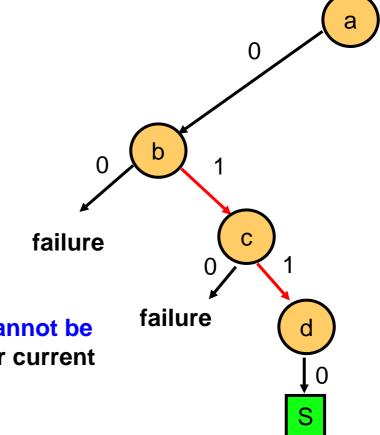

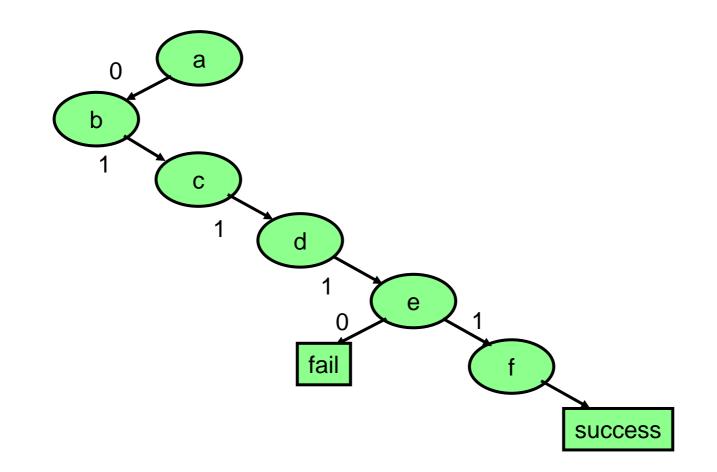

### **Decision Tree in PODEM**

- Decision node: the PI selected through backtrace for value assignment

- Branch: the value assignment to the selected PI

# **Terminating Conditions**

- D-algorithm

- Success:

- (1) Fault effect at an output (D-frontier may not be empty)

- (2) J-frontier is empty

- Failure:

- (1) D-frontier is empty (all possible paths are false)

- (2) J-frontier is not empty

- PODEM

- Success:

- Fault effect seen at an output

- Failure:

- Every PI assignment leads to failure, in which D-frontier is empty while fault has been activated

```

PODEM () /* using depth-first-search */

```

begin

```

If(error at PO) return(SUCCESS);

If(test not possible) return(FAILURE);

(k, v_k) = Objective();

/* choose a line to be justified */

(j, v_i) = Backtrace(k, v_k); /* choose the PI to be assigned */

Imply (j, v_i);

/* make a decision */

If ( PODEM()==SUCCESS ) return (SUCCESS);

Imply (j, v_i');

/* reverse decision */

If ( PODEM()==SUCCESS ) return(SUCCESS);

Imply (j, x);

What PI to assign ?

Return (FAILURE);

end

J=V<sub>i</sub>

|=V

Recursive-call

Recursive-call

If necessary

```

### **Overview of PODEM**

- PODEM

- examines all possible input patterns implicitly but exhaustively (branch-and-bound) for finding a test

- It is complete like D-algorithm (I.e., will find one if a test exists)

- Other Key Features

- No J-frontier, since there are no values that require justification

- No consistency check, as conflicts can never occur

- No backward implication, because values are propagated only forward

- Backtracking is implicitly done by simulation rather than by an explicit and time-consuming save/restore process

- Experimental results show that PODEM is generally faster than the D-algorithm

# The Selection Strategy in PODEM

- In Objective() and Backtrace()

- Selections are done arbitrarily in original PODEM

- The algorithm will be more efficient if certain guidance used in the selections of objective node and backtrace path

- Selection Principle

- Principle 1: Among several unsolved problems

- $\rightarrow$  Attack the hardest one

- Ex: to justify a '1' at an AND-gate output

- Principle 2: Among several solutions for solving a problem

- $\rightarrow$  Try the easiest one

- Ex: to justify a '1' at OR-gate output

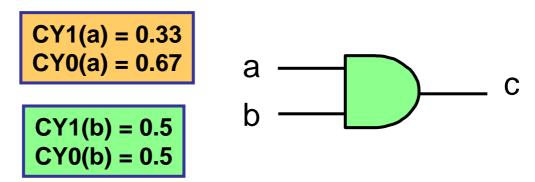

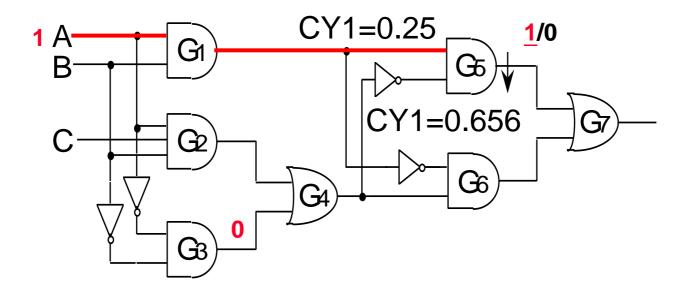

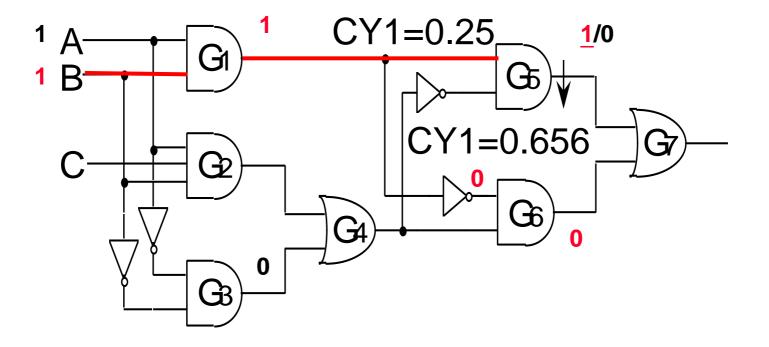

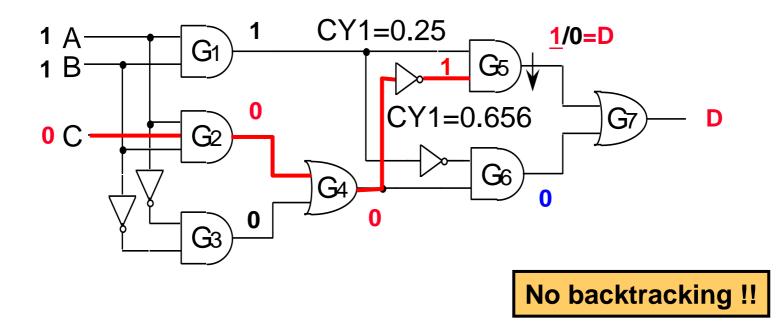

### **Controllability As Guidance**

- Controllability of a signal w

- CY1(w): the probability that line w has value 1.

- CYO(w): the probability that line w has value 0.

- Example:

- f = ab

- Assume CY1(a)=CY0(a)=CY1(b)=CY0(b)=0.5

- $\rightarrow$  CY1(f)=CY1(a)xCY1(b)=0.25,

- $\rightarrow$  CY0(f)=CY0(a)+CY0(b)-CY0(a)xCY0(b)=0.75

- Example of Smart Backtracing

- Objective (c, 1)  $\rightarrow$  choose path c $\rightarrow$ a for backtracing

- Objective (c, 0)  $\rightarrow$  choose path c $\rightarrow$ a for backtracing

# **Testability Analysis**

- Applications

- To give an early warning about the testing problems that lie ahead

- To provide guidance in ATPG

- Complexity

- Should be simpler than ATPG and fault simulation, I.e., need to be linear or almost linear in terms of circuit size

- Topology analysis

- Only the structure of the circuit is analyzed

- No test vectors are involved

- Only approximate, reconvergent fanouts cause inaccuracy

#### SCOAP

#### (Sandia Controllability/Observability Analysis Program)

- Computes six numbers for each node N

- CC<sup>0</sup>(N) and CC<sup>1</sup>(N)

- Combinational 0 and 1 controllability of a node N

- SC<sup>0</sup>(N) and SC<sup>1</sup>(N)

- Sequential 0 and 1 controllability of a node N

- CO(N)

- Combinational observability

- \_ SO(N)

- Sequential observability

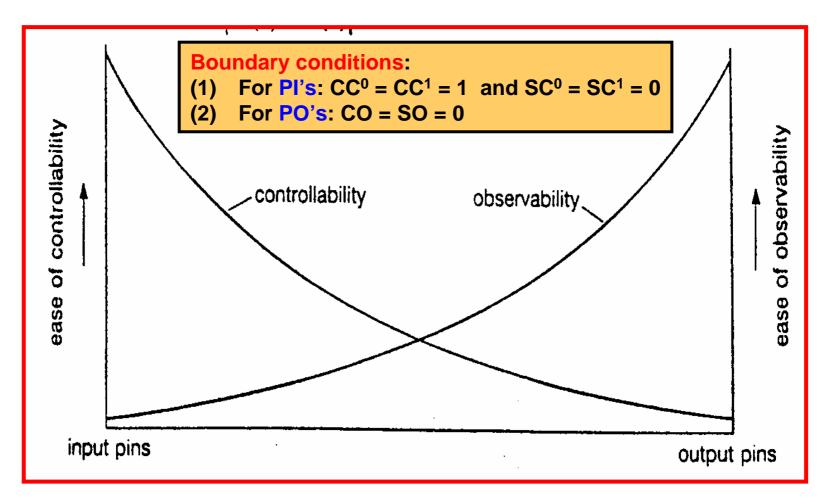

#### General Characteristic of Controllability and Observability

Controllability calculation: sweeping the circuit from PI to PO Observability calculation: sweeping the circuit from PO to PI

### **Controllability Measures**

- CC<sup>0</sup>(N) and CC<sup>1</sup>(N)

- The number of combinational nodes that must be assigned values to justify a 0 or 1 at node N

- SC<sup>0</sup>(N) and SC<sup>1</sup>(N)

- The number of sequential nodes that must be assigned values to justify a 0 or 1 at node N

$$\begin{split} &CC^0(Y) = min \left[CC^0(x1) \ , \ CC^0(x2) \ \right] + 1 \\ &CC^1(Y) = CC^1(x1) + CC^1(x2) + 1 \\ &SC^0(Y) = min \left[SC^0(x1) \ , \ SC^0(x2) \ \right] \\ &SC^1(Y) = SC^1(x1) + SC^1(x2) \end{split}$$

### **Controllability Measure (con't)**

- CC<sup>0</sup>(N) and CC<sup>1</sup>(N)

- The number of combinational nodes that must be assigned values to justify a 0 or 1 at node N

- SC<sup>0</sup>(N) and SC<sup>1</sup>(N)

- The number of sequential nodes that must be assigned values to justify a 0 or 1 at node N

$$\begin{array}{c} x_1 \\ x_2 \\ x_3 \end{array} \longrightarrow Y$$

$$\begin{split} &CC^0(Y) = CC^0(x1) + CC^0(x2) + CC^0(x3) + 1 \\ &CC^1(Y) = \min \left[ \ CC^1(x1), \ CC^1(x2), \ CC^1(x3) \ \right] + 1 \\ &SC^0(Y) = SC^0(x1) + SC^0(x2) + SC^0(x3) \\ &SC^1(Y) = \min \left[ \ SC^1(x1), \ SC^1(x2), \ SC^1(x3) \ \right] \end{split}$$

- CO(N) and SO(N)

- The observability of a node N is a function of the output observability and of the cost of holding all other inputs at non-controlling values

$$\begin{array}{c} x_1 \\ x_2 \\ x_3 \end{array} \longrightarrow Y$$

$$\begin{aligned} CO(x1) &= CO(Y) + CC^0(x2) + CC^0(x3) + 1\\ SO(x1) &= SO(Y) + SC^0(x2) + SC^0(x3) \end{aligned}$$

Initial objective=(G5,1). G5 is an AND gate  $\rightarrow$  Choose the hardest-1  $\rightarrow$  Current objective=(G1,1). G1 is an AND gate  $\rightarrow$  Choose the hardest-1  $\rightarrow$  Arbitrarily, Current objective=(A,1). A is a PI  $\rightarrow$  Implication  $\rightarrow$  G3=0.

#### PODEM: Example 2 (2/3)

The initial objective satisfied? No!  $\rightarrow$  Current objective=(G5,1). G5 is an AND gate  $\rightarrow$  Choose the hardest-1  $\rightarrow$  Current objective=(G1,1). G1 is an AND gate  $\rightarrow$  Choose the hardest-1  $\rightarrow$  Arbitrarily, Current objective=(B,1). B is a PI  $\rightarrow$  Implication  $\rightarrow$  G1=1, G6=0.

The initial objective satisfied? No!  $\rightarrow$  Current objective=(G5,1). The value of G1 is known  $\rightarrow$  Current objective=(G4,0). The value of G3 is known  $\rightarrow$  Current objective=(G2,0). A, B is known  $\rightarrow$  Current objective=(C,0). C is a PI  $\rightarrow$  Implication  $\rightarrow$  G2=0, G4=0, G5=D, G7=D.

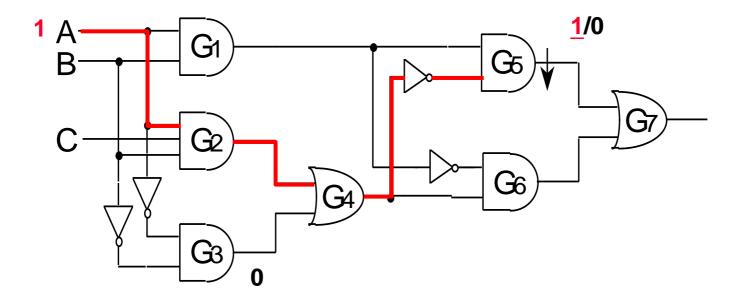

#### If The Backtracing Is Not Guided (1/3)

Initial objective=(G5,1). Choose path G5-G4-G2-A  $\rightarrow$  A=0. Implication for A=0  $\rightarrow$  G1=0, G5=0  $\rightarrow$  Backtracking to A=1. Implication for A=1  $\rightarrow$  G3=0.

### If The Backtracing Is Not Guided (2/3)

The initial objective satisfied? No!  $\rightarrow$  Current objective=(G5,1). Choose path G5-G4-G2-B  $\rightarrow$  B=0. Implication for B=0  $\rightarrow$  G1=0, G5=0  $\rightarrow$  Backtracking to B=1. Implication for B=1  $\rightarrow$  G1=1, G6=0.

#### If The Backtracing Is Not Guided (3/3)

The initial objective satisfied? No!  $\rightarrow$  Current objective=(G5,1). Choose path G5-G4-G2-C  $\rightarrow$  C=0. Implication for C=0  $\rightarrow$  G2=0, G4=0, G5=D, G7=D.

Two times of backtracking !!

### Outline of ATPG (Automatic Test Pattern Generation)

- Test Generation (TG) Methods

- Based on Truth Table

- Based on Boolean Equation

- Based on Structural Analysis

- D-algorithm [Roth 1967]

- 9-Valued D-algorithm [Cha 1978]

- PODEM [Goel 1981]

- FAN [Fujiwara 1983]

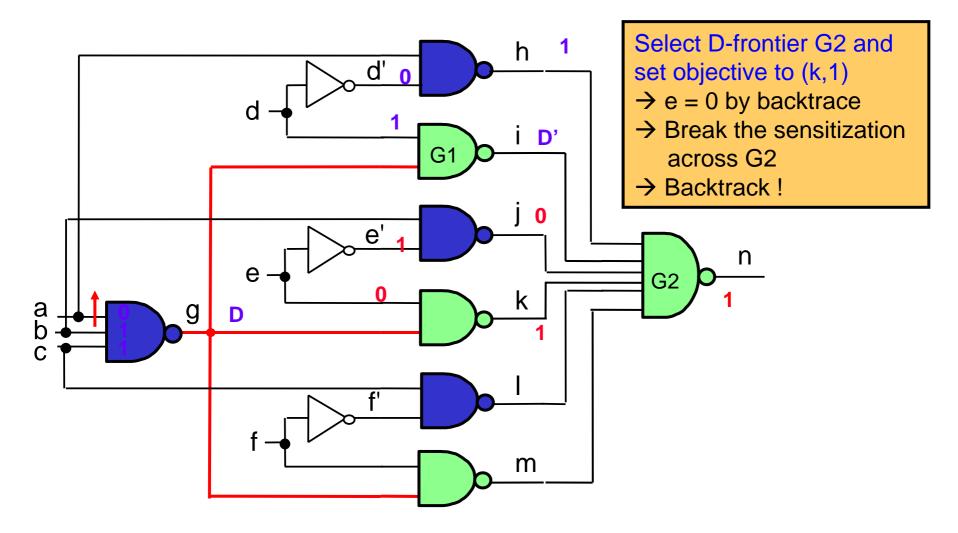

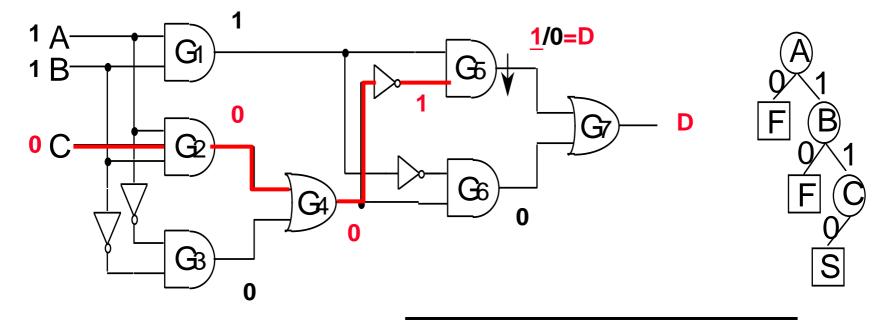

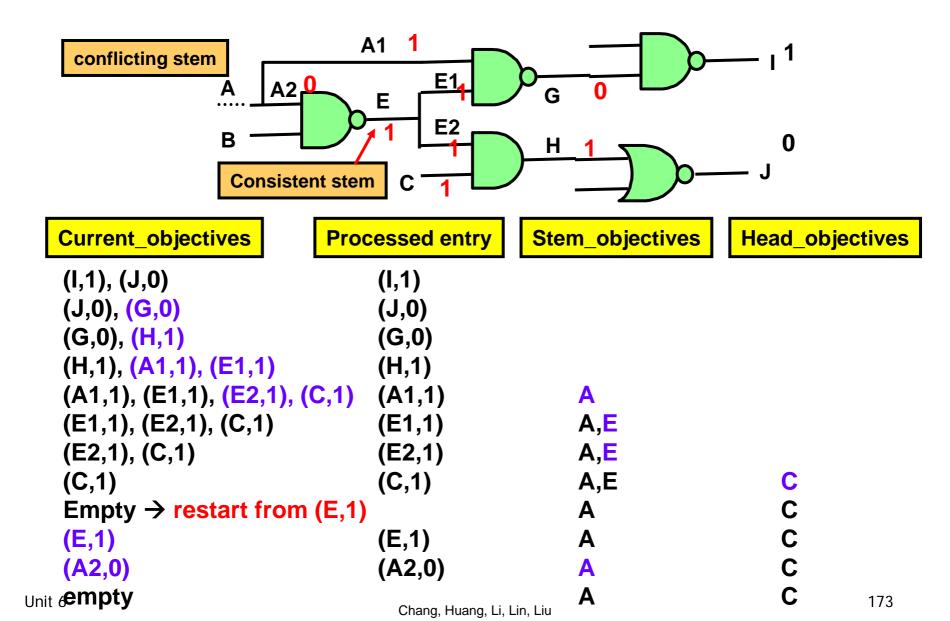

# FAN (Fanout Oriented) Algorithm

- FAN

- Introduces two major extensions to PODEM's backtracing algorithm

- 1st extension

- Rather than stopping at PI's, backtracing in FAN may stop at an internal lines

- 2nd extension

- FAN uses multiple backtrace procedure, which attempts to satisfy a set of objectives simultaneously

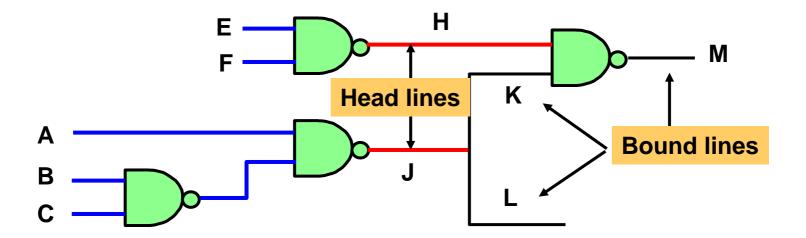

### **Headlines and Bound Lines**

- Bound line

- A line reachable from at least one stem

- Free line

- A line that is NOT bound line

- Head line

- A free line that directly feeds a bound line

### **Decision Tree (PODEM v.s. FAN)**

# Why Stops at Head Lines ?

- Head lines are mutually independent

- Hence, for each given value combination at head lines, there always exists an input combination to realize it.

- FAN has two-steps

- Step 1: PODEM using headlines as pseudo-PI's

- Step 2: Generate real input pattern to realize the value combination at head lines.

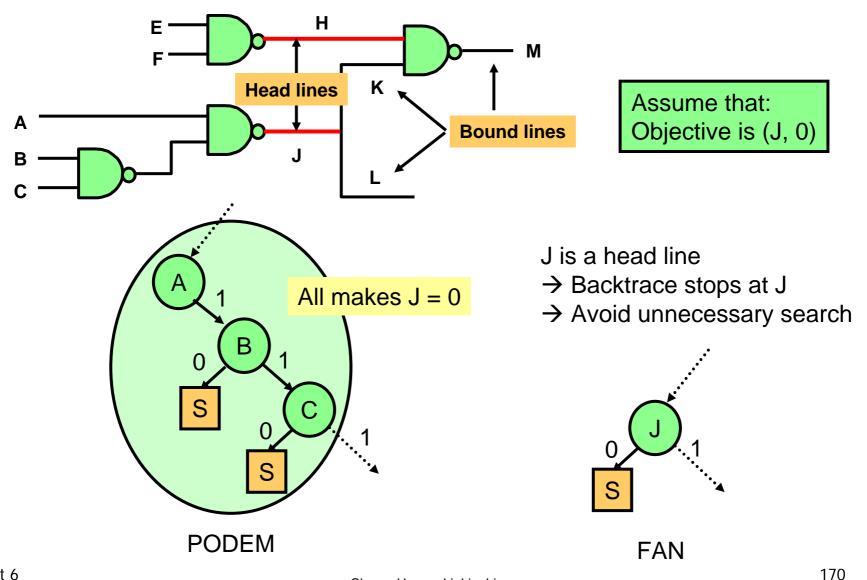

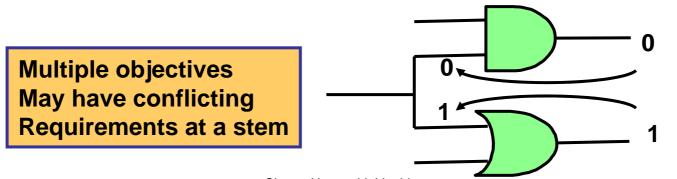

# Why Multiple Backtrace ?

- Drawback of Single Backtrace

- A PI assignment satisfying one objective → may preclude achieving another one, and this leads to backtracking

- Multiple Backtrace

- Starts from a set of objectives (Current\_objectives)

- Maps these multiple objectives into a head-line assignment k=v<sub>k</sub> that is likely to

- Contribute to the achievement of a subset of the objectives

- Or show that some subset of the original objectives cannot be simultaneously achieved

### **Example: Multiple Backtrace**

### **References For ATPG**

- [1] Sellers et al., "Analyzing errors with the Boolean difference", IEEE Trans. Computers, pp. 676-683, 1968.

- [2] J. P. Roth, "Diagnosis of Automata Failures: A Calculus and a Method", IBM Journal of Research and Development, pp. 278-291, July, 1966.

- [2'] J. P. Roth et al., "Programmed Algorithms to Compute Tests to Detect and Distinguish Between Failures in Logic Circuits", IEEE Trans. Electronic Computers, pp. 567-579, Oct. 1967.

- [3] C. W. Cha et al, "9-V Algorithm for Test Pattern Generation of Combinational Digital Circuits", IEEE TC, pp. 193-200, March, 1978.

- [4] P. Goel, "An Implicit Enumeration Algorithm to Generate Tests for Combinational Logic Circuits", IEEE Trans. Computers, pp. 215-222, March, 1981.

- [5] H. Fujiwara and T. Shimono, "On the Acceleration of Test Generation Algorithms", IEEE TC, pp. 1137-1144, Dec. 1983.

- [6] M. H. Schulz et al., "SOCRATES: A Highly Efficient Automatic Test Pattern Generation System", IEEE Trans. on CAD, pp. 126-137, 1988.

- [6'] M. H. Schulz and E. Auth, "Improved Deterministic Test Pattern Generation with Applications to Redundancy Identification", IEEE Trans CAD, pp. 811-816, 1989.

# Outline

- Introduction

- Fault Modeling

- Fault Simulation

- Test Generation

- Design For Testability

# Why DFT ?

- Direct Testing is Way Too Difficult !

- Large number of FFs

- Embedded memory blocks

- Embedded analog blocks

# Design For Testability is inevitable

Like death and tax

# **Design For Testability**

- Definition

- Design For Testability (DFT) refers to those design techniques that make test generation and testing costeffective

- DFT Methods

- Ad-hoc methods

- Scan, full and partial

- Built-In Self-Test (BIST)

- Boundary scan

- Cost of DFT

- Pin count, area, performance, design-time, test-time

### **Important Factors**

- Controllability

- Measure the ease of controlling a line

- Observability

- Measure the ease of observing a line at PO

- Predictability

- Measure the ease of predicting output values

- DFT deals with ways of improving

- Controllability

- Observability

- Predictability

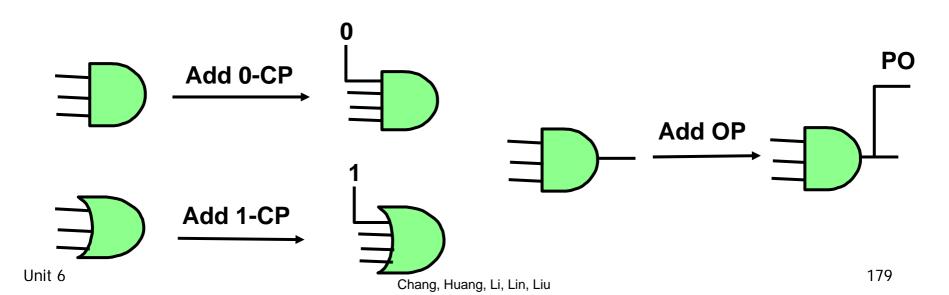

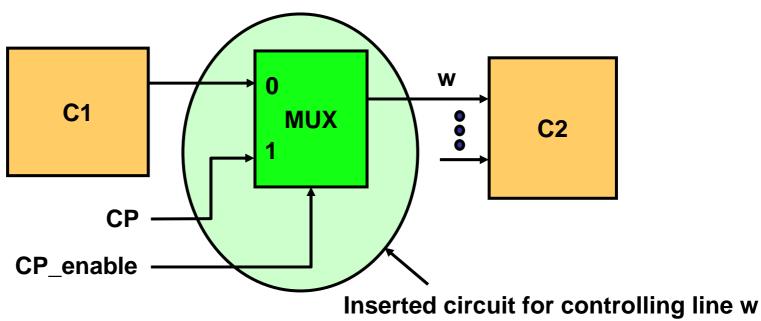

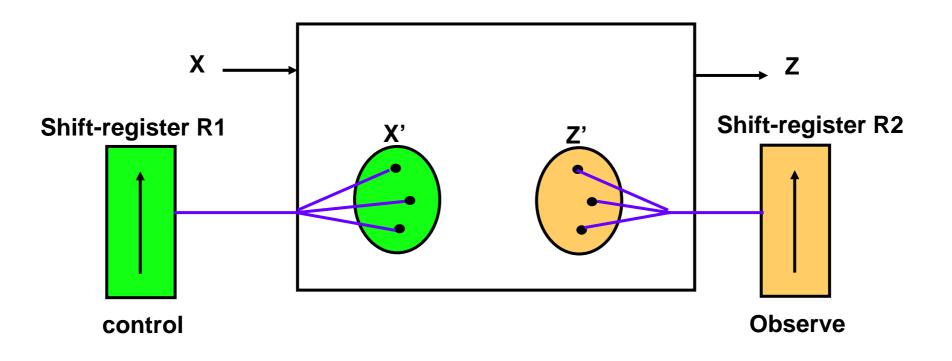

### **Test Point Insertion**

- Employ test points to enhance

- Controllability

- Observability

- CP: Control Points

- Primary inputs used to enhance controllability

- OP: Observability Points

- Primary outputs used to enhance observability

# **0/1 Injection Circuitry**

- Normal operation When CP\_enable = 0

- Inject 0

- Set CP\_enable = 1 and CP = 0

- Inject 1

- Set CP\_enable = 1 and CP = 1

# **Control Point Selection**

- Impact

- The controllability of the fanout-cone of the added point is improved

- Common selections

- Control, address, and data buses

- Enable / Hold inputs

- Enable and read/write inputs to memory

- Clock and preset/clear signals of flip-flops

- Data select inputs to multiplexers and demultiplexers

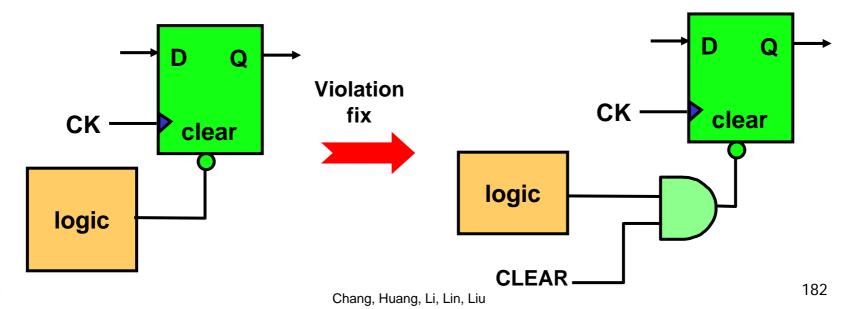

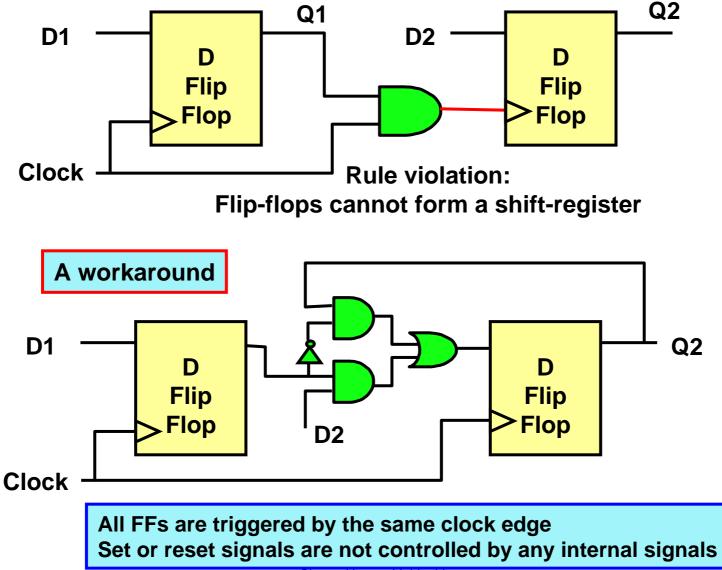

# **Example: Use CP to Fix DFT Rule Violation**

- DFT rule violations

- The set/clear signal of a flip-flop is generated by other logic, instead of directly controlled by an input pin

- Gated clock signals

- Violation Fix

– Add a control point to the set/clear signal or clock signals

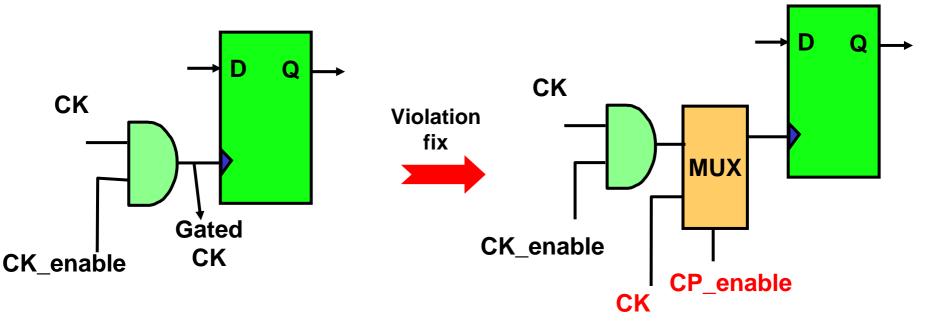

# **Example: Fixing Gated Clock**

- Gated Clocks

- Advantage: power dissipation of a logic design can thus reduced

- Drawback: the design's testability is also reduced

- Testability Fix

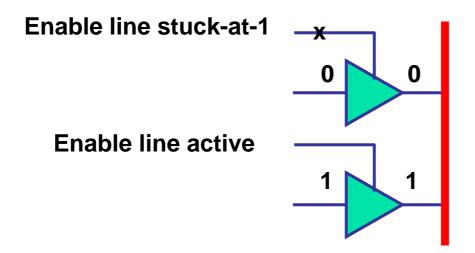

## **Example: Fixing Tri-State Bus Contention**

- Bus Contention

- A stuck-at-fault at the tri-state enable line may cause bus contention – multiple active drivers connect to the bus simultaneously

- Fix

- Add CP's to turn off tri-state devices during testing

Unpredicted voltage on bus may cause fault to go unnoticed

#### **Observation Point Selection**

- Impact

- The observability of the transitive fanins of the added point is improved

- Common choice

- Stem lines having high fanout

- Global feedback paths

- Redundant signal lines

- Output of logic devices having many inputs

- MUX, XOR trees

- Output from state devices

- Address, control and data buses

#### **Problems of CP & OP**

- Large number of I/O pins

- Add MUX's to reduce the number of I/O pins

- Serially shift CP values by shift-registers

- Larger test time

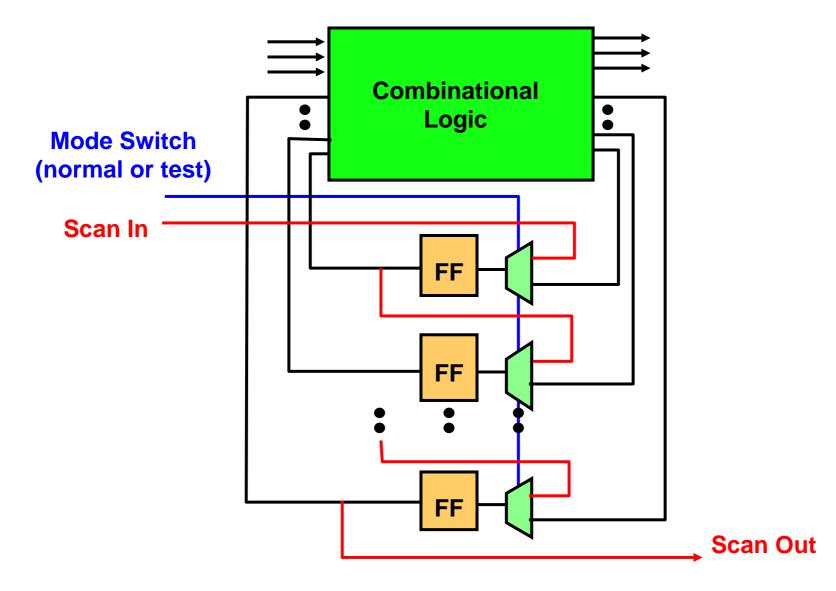

- Objective

- To provide controllability and observability at internal state variables for testing

- Method

- Add test mode control signal(s) to circuit

- Connect flip-flops to form shift registers in test mode

- Make inputs/outputs of the flip-flops in the shift register controllable and observable

- Types

- Internal scan

- Full scan, Partial scan, Random access

- Boundary scan

#### **The Scan Concept**

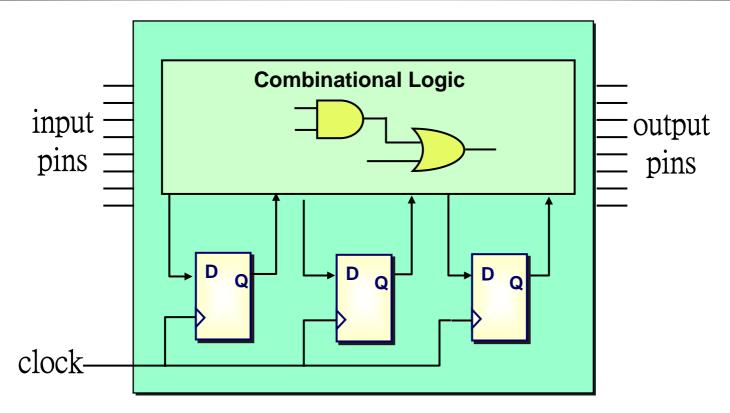

# **A Logic Design Before Scan Insertion**

#### <u>Sequential ATPG</u> is extremely difficult: due to the lack of controllability and observability at flip-flops.

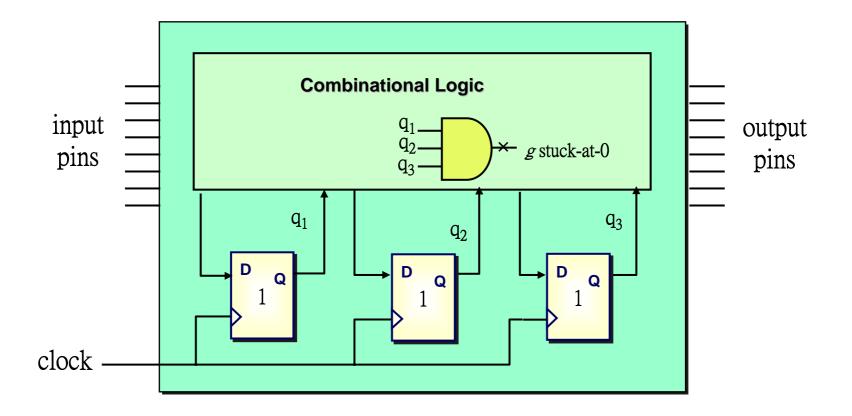

#### **Example: A 3-stage Counter**

It takes 8 clock cycles to set the flip-flops to be (1, 1, 1), for detecting the target fault *g* stuck-at-0 fault (2<sup>20</sup> cycles for a 20-stage counter !)

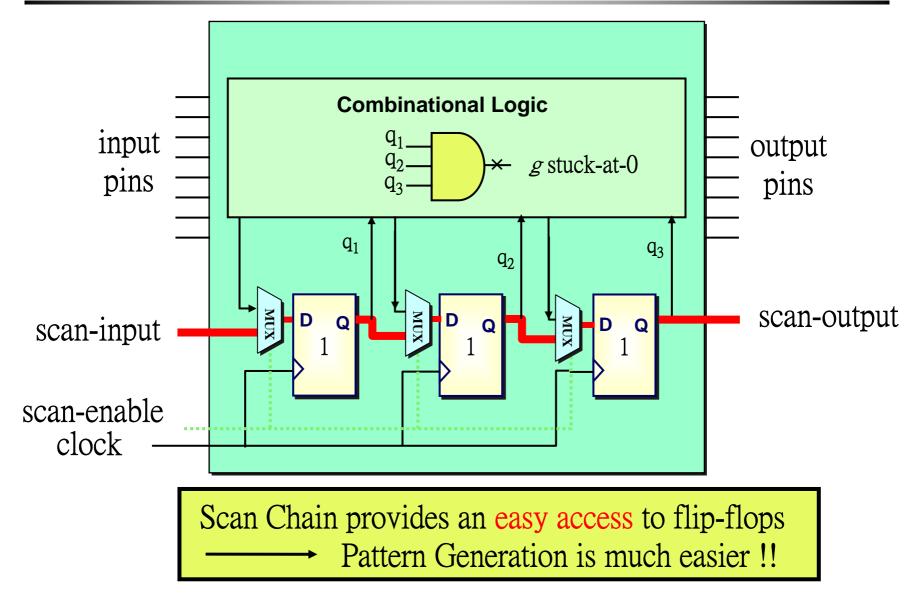

# **A Logic Design After Scan Insertion**

# **Procedure Of Applying Test Patterns**

- Notation

- Test vectors  $T = \langle t_i^I, t_i^F \rangle i = 1, 2, ...$

- Output Response  $\mathbf{R} = \langle \mathbf{r}_i^0, \mathbf{r}_i^F \rangle \mathbf{i} = 1, 2, ...$

- Test Application

- (1) i = 1;

- (2) Scan-in t<sub>1</sub><sup>F</sup> /\* scan-in the first state vector for PPI's \*/

- (3) Apply t<sup>I</sup><sub>i</sub> /\* apply current input vector at PI's \*/

- (4) Observe  $\ r_i^{\ 0}$   $\ /*$  observe current output response at PO's \*/

- (5) Parallelly load register /\* load-in the next vector at PPO's \*/

- (I.e., set Mode to 'Normal')

- = (6) Scan-out  $r_i^F$  while scanning-in  $t_{i+1}^F/*$  overlap scan-in and scan-out \*/

- (7) i = i+1; Goto step (3)

# **Testing Scan Chain ?**

- Common practice

- Scan chain is often first tested before testing core logic by pumping-in and pumping-out random vectors

- Procedure

- \_ (1) i = 0;

- (2) Scan-in 1<sup>st</sup> random vector to flip-flops

- (3) Scan-out (i)<sup>th</sup> random vector while scanning-in (i+1)<sup>th</sup> vector for flip-flops.

- The (i)<sup>th</sup> scan-out vector should be identical to (i)<sup>th</sup> vector scanned in earlier, otherwise scan-chain is mal-functioning

- \_ (4) If necessary i = i+1, goto step (3)

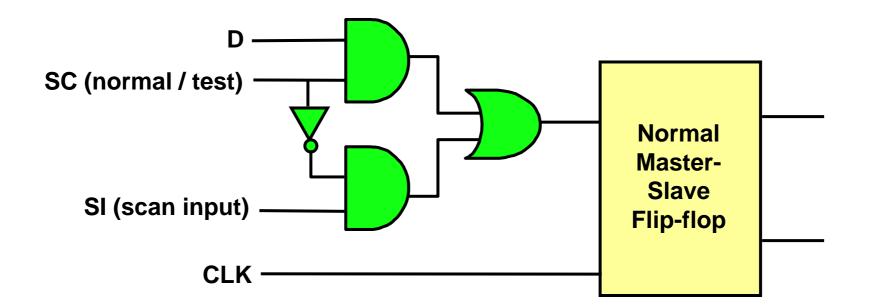

## **MUXed Scan Flip-Flop**

- Only D-type master-slave flip-flops are used

- One extra primary input pin available for test

- All flip-flop clocks controlled from primary inputs

- No gated clock allowed

- Clocks must not feed data inputs of flip-flops

- Most popularly supported in standard cell libraries

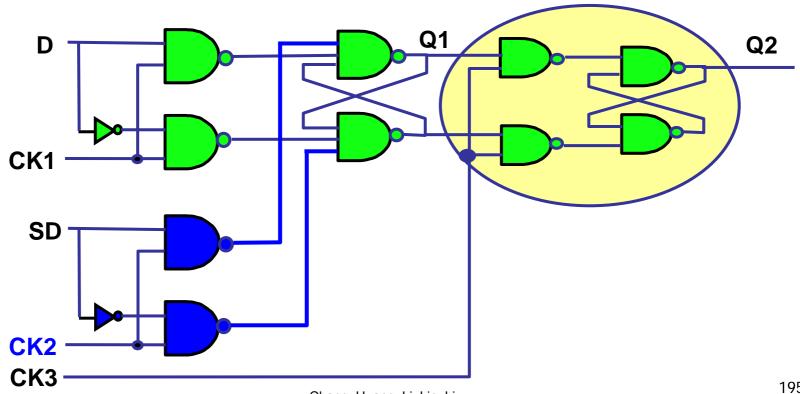

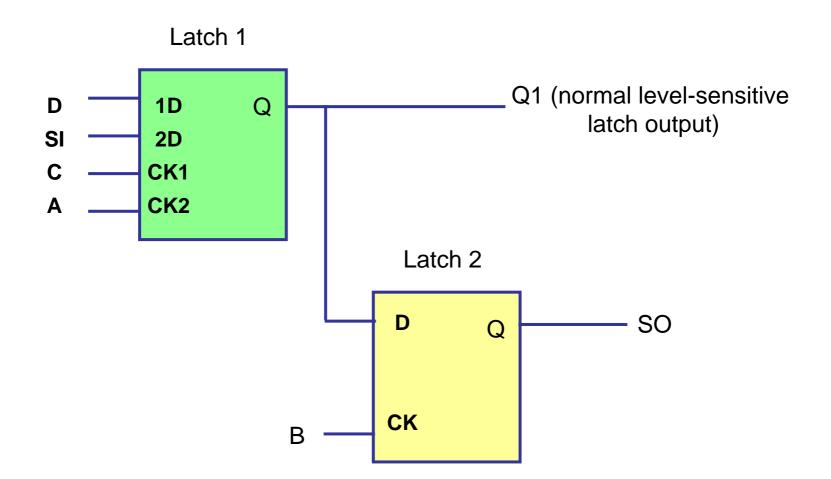

# LSSD Scan flip-flop (1977 IBM)

LSSD: Level Sensitive Scan Design

Less performance degradation than MUXed scan FF

Clocking

Unit 6

- Normal operation: non-overlapping CK1=1  $\rightarrow$  CK3=1

- Scan operation: non-overlapping CK2=1  $\rightarrow$  CK3=1

#### **Scan Rule Violation Example**

#### **Some Problems With Full Scan**

• Problems

Major Commercial Test Tool Companies Synopsys Mentor-Graphics SynTest (華騰科技) LogicVision

- Area overhead

- Possible performance degradation

- High test application time

- Power dissipation

- Features of Commercial Tools

- Scan-rule violation check (e.g., DFT rule check)

- Scan insertion (convert a FF to its scan version)

- ATPG (both combinational and sequential)

- Scan chain reordering after layout

#### **Performance Overhead**

- The increase of delay along the normal data paths include:

- Extra gate delay due to the multiplexer

- Extra delay due to the capacitive loading of the scan-wiring at each flip-flop's output

- Timing-driven partial scan

- Try to avoid scan flip-flops that belong to the timing critical paths

- The flip-flop selection algorithm for partial scan can take this into consideration to reduce the timing impact of scan to the design

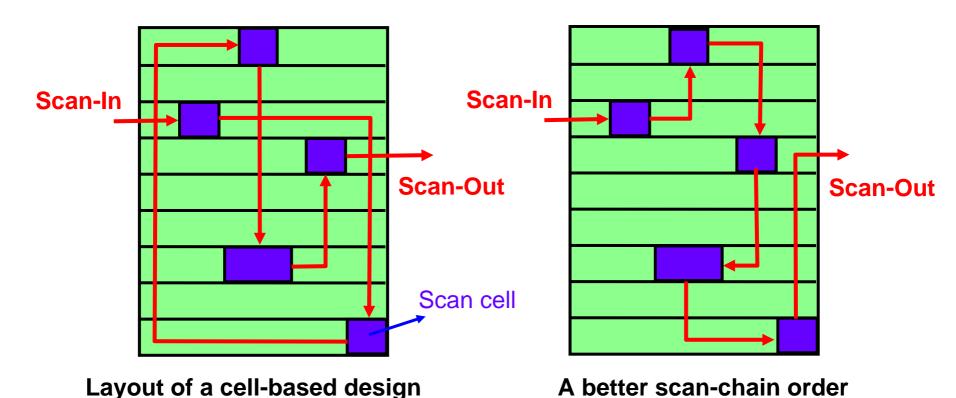

### **Scan-Chain Reordering**

- Scan-chain order is often decided at gate-level without knowing the cell placement

- Scan-chain consumes a lot of routing resources, and could be minimized by re-ordering the flip-flops in the chain after layout is done

#### **Overhead of Scan Design**

- No. of CMOS gates = 2000

- Fraction of flip-flops = 0.478

- Fraction of normal routing = 0.471

| Scan<br>implementation | Predicted<br>overhead | Actual area<br>overhead | Normalized operating<br>frequency |

|------------------------|-----------------------|-------------------------|-----------------------------------|

| None                   | 0                     | 0                       | 1.0                               |

| Hierarchical           | 14.05%                | 16.93%                  | 0.87                              |

| Optimized              | 14.05%                | 11.9%                   | 0.91                              |

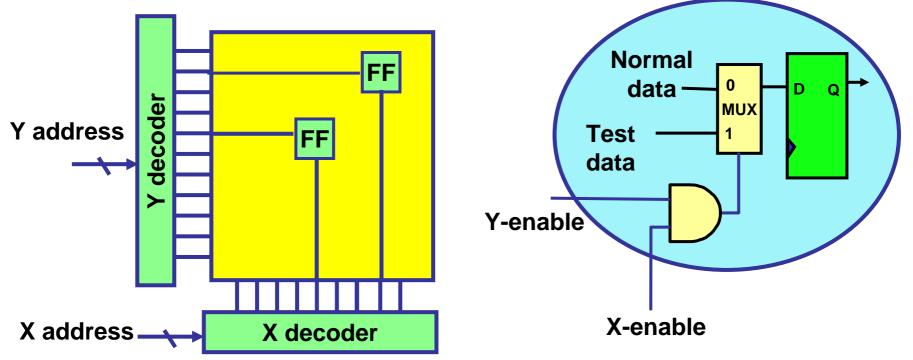

# **Random Access Scan**

- Comparison with Scan-Chain

- More flexible any FF can be accessed in constant time

- Test time could be reduced

- More hardware and routing overhead

#### **Parameters**

#### • link\_library

- The ASIC vendor library where you design is initially represented

- target\_library

- Usually the same as your link\_library, unless you are translating a design between technologies

- test\_default\_scan\_style

- \_ multiplexed\_flip\_flop, clocked\_scan, aux\_clock\_lssd

- Note that: the cell library incorporated should support these scan cells

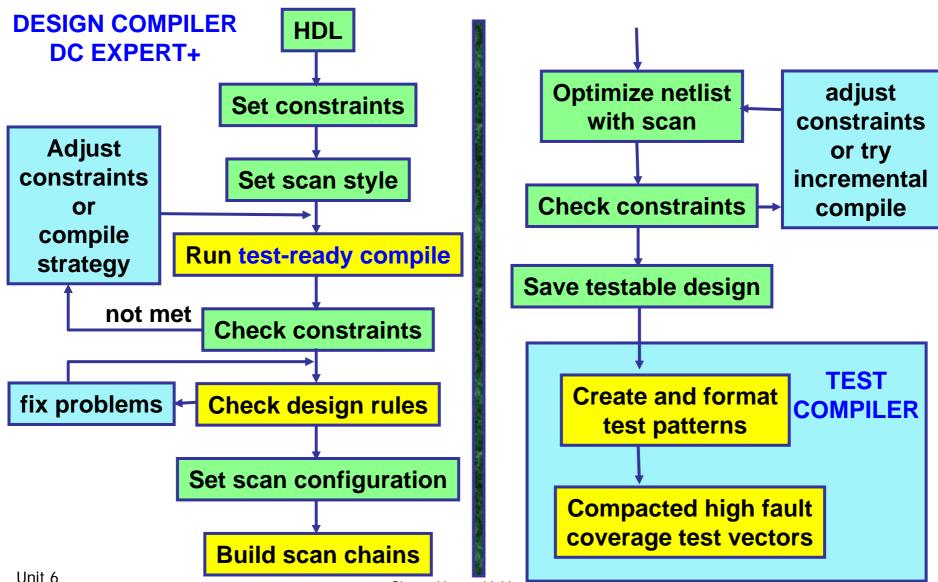

# **Typical Flat Design Flow**

# **Synthesizing The Design**

• Read in HDL code

dc\_shell > read –format verilog design\_name.v

• Set target\_library

dc\_shell > target\_library = asic\_vendor.db

• Constraint the design

dc\_shell > max\_area 1000

dc\_shell > create\_clock clock\_port -period 20 -waveform {10,15}

- Declare the test methodology dc\_shell > set\_scan\_configuration –methodology partial\_scan

- Select scan style

dc\_shell > test\_default\_scan\_style = multiplexed\_flip\_flop

• Compilation

dc\_shell > compile -scan

# Synthesizing The Design (con't)

• Check constraints

dc\_shell > report\_constraint –all\_violators

• Save design

dc\_shell > write --format db --out design\_test\_ready.db

• Check design rules

dc\_shell > check\_test

# **Building Scan Chains**

- Declare Scan Enable Signal dc\_shell > set\_scan\_signal test\_scan\_enable --port SE dc\_shell > set\_drive 2 SE

- Set Min. Fault Coverage If Partial Scan dc\_shell > set\_min\_fault\_coverage 95

- No Scan Replacement dc\_shell > set\_scan\_configuration –replace false

- Build the Scan Chains dc\_shell > insert\_scan

- Check the Design Rules Again dc\_shell > check\_test

#### **Generating Test Patterns**

- Generate Test Report dc\_shell > report\_test -scan\_path

- Write out Scan Design dc\_shell > write –format db –hierarchy –out design.db

- Generate The Test

dc\_shell > create\_test\_patterns -compact\_effort high

- Write Out Test Patterns dc\_shell > write\_test -out test\_vectors -format WGL

- WGL (Waveform Generation Language)

- Is a format supported by Summit Design Software

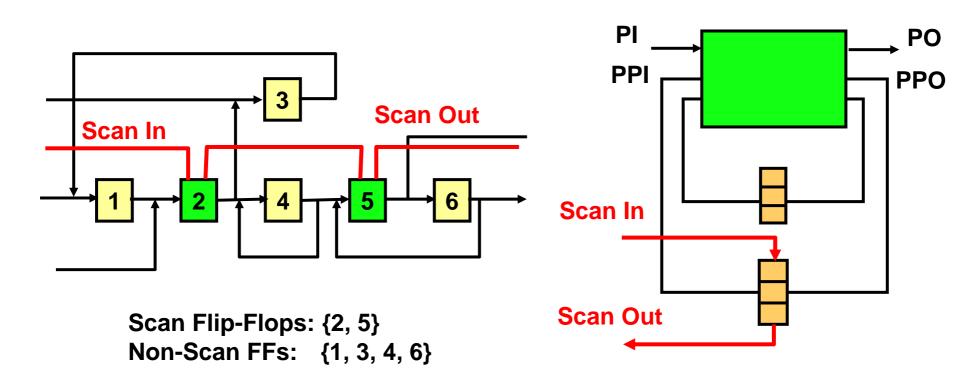

#### **Partial Scan**

- Basic idea

- Select a subset of flip-flops for scan

- Lower overhead (area and speed)

- Relaxed design rules

- Cycle-breaking technique

- Cheng & Agrawal, IEEE Trans. On Computers, April 1990

- Select scan flip-flops to simplify sequential ATPG

- Overhead is about 25% off than full scan

- Timing-driven partial scan

- Jou & Cheng, ICCAD, Nov. 1991

- Allow optimization of area, timing, and testability simultaneously

#### **Full Scan vs. Partial Scan**

every flip-flop is a scan-FF NOT every flip-flop is a scan-FF

| test time         | longer | shorter       |

|-------------------|--------|---------------|

| hardware overhead | more   | less          |

| fault coverage    | ~100%  | unpredictable |

| ease-of-use       | easier | harder        |

#### **Partial Scan Design**

# **Cycle Breaking Algorithm**

- Algorithm 1

- Select nodes in a digraph G=(V,E) to cut all cycles of length greater than one

- Step 1

- Find all the non-trivial SCCs  $G_i = (V_i, E_i)$ , where  $1 \le i \le r$

- If no non-trivial SCC stop

- Step 2

- (1) Delete a node v using one of the heuristics H1, H2, H3 (to be discussed later)

- (2) Delete node v from  $V_i$  and delete all incoming and outgoing edges of v

- (3) Let the resulting graph be  $G_i' = (V_i', E_i')$

- Execute Algorithm 1 recursively with G<sub>i</sub>' as input graph

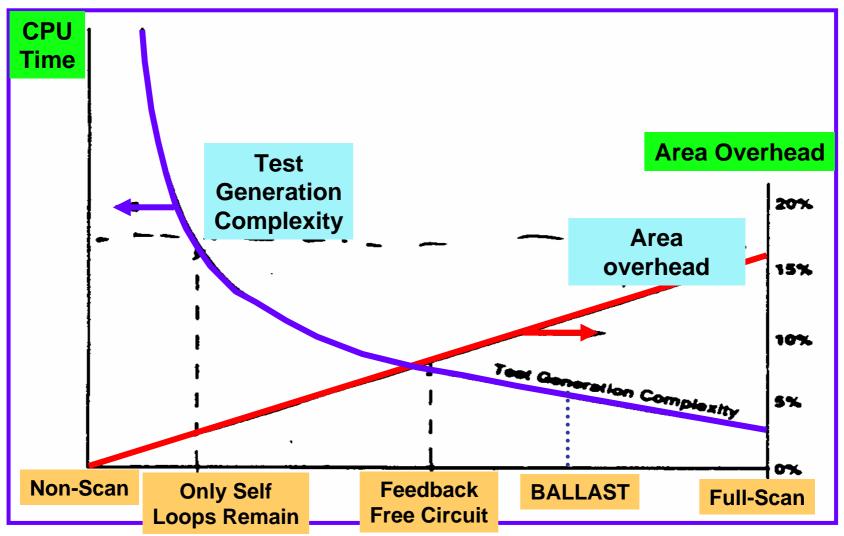

#### Reducing the Length of Consecutive Self-Loop Paths

- Definition

- A graph has a consecutive self-loop path of length K if there exists a directed path of exactly K vertices, each having a self-loop

- Observation

- Circuits with consecutive self-loop paths, such as counters, need longer test generation time

- Solution

- Reduce the length of consecutive self-loop paths by scanning some of the flip-flops with self-loops

#### Trade-Off of Area Overhead v.s. Test Generation Effort

# Conclusions

- Testing

- Conducted after manufacturing

- Must be considered during the design process

- Major Fault Models

- Stuck-At, Bridging, Stuck-Open, Delay Fault, ...

- Major Tools Needed

- Design-For-Testability

- By Scan Chain Insertion or Built-In Self-Test

- Fault Simulation

- Automatic Test Pattern Generation

- Other Applications in CAD

- ATPG is a way of Boolean Reasoning, applicable to may logic-domain CAD problems